10 А = 1 нм = 8 атомів кремнію в ряд

Последние статьи и обзоры

Новости

TSMC отримає літографічні машини High-NA EUV від ASML до кінця року

-

KimRomik

Member

Предлагаю обсудить TSMC отримає літографічні машини High-NA EUV від ASML до кінця року

10 А = 1 нм = 8 атомів кремнію в ряд

10 А = 1 нм = 8 атомів кремнію в ряд

-

taras_cs

Member

- Откуда: Варшава-Київ-Дніпро

Тут головне - хто і як рахує

Відправлено через 4 хвилини 6 секунд:

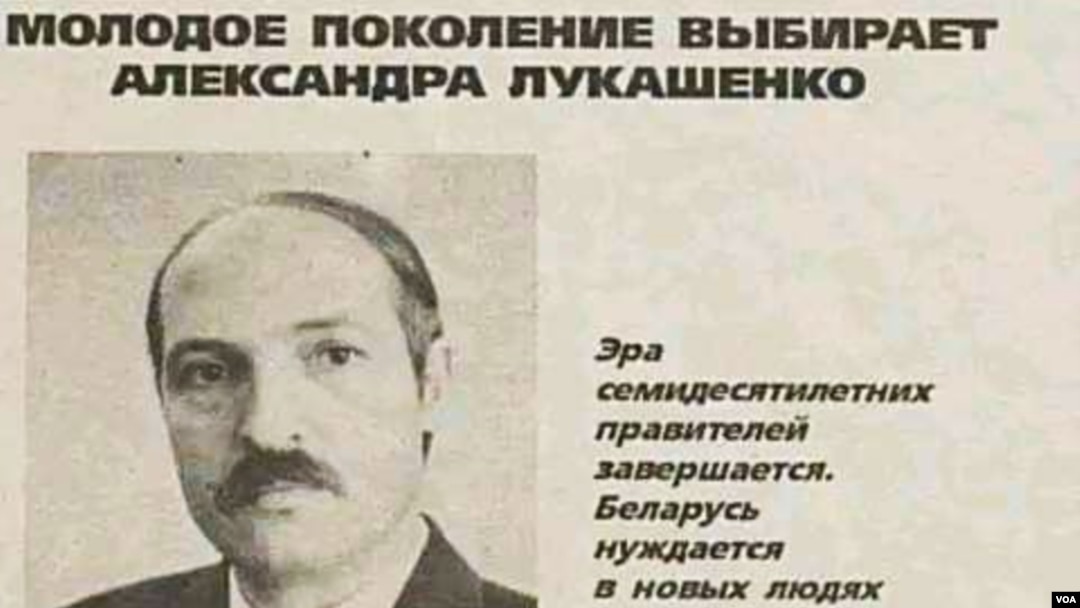

Не маю нічого проти. Росіян теж за людей вважали, а виявилось, що будь-який диктатор після 10 років при владі починає або війни або погрожувати сусідам (коли воювати не має чим).Інтерес до нового обладнання мають китайські замовники, але воно їм недоступне через санкції США та заборону на продаж до Китаю.

- спойлер

-

ASTON

Member

- Откуда: Kharkiv

Аби Кітаю не продавали наничку.

Бо задовбали ці диктатури - і так життя складне було, вони його взагалі на нуль перемножили.

Тож поки будуть диктатури - тре їм забороняти розвиток взагалі. Хай сам щось вигадують. А то крадуть все і купляють на чорному ринку.

Бо задовбали ці диктатури - і так життя складне було, вони його взагалі на нуль перемножили.

Тож поки будуть диктатури - тре їм забороняти розвиток взагалі. Хай сам щось вигадують. А то крадуть все і купляють на чорному ринку.

-

EvhenS

Member

- Откуда: Черкаси

KimRomik

Колись читав що реальний розмір транзистора так і залишився в районі 30-45нм. Там тунельні ефекти і інші телепорти електронів по ізолятору не дають зробити робочий пристрій. Просто примудряються пакувати транзистори плотніше, а для цього треба якось новий процес називати щоб було видно що він кращий. Тому маркетингові нанометри зменшилися до зовсім оковирних (для знаючих людей) величин.

Колись читав що реальний розмір транзистора так і залишився в районі 30-45нм. Там тунельні ефекти і інші телепорти електронів по ізолятору не дають зробити робочий пристрій. Просто примудряються пакувати транзистори плотніше, а для цього треба якось новий процес називати щоб було видно що він кращий. Тому маркетингові нанометри зменшилися до зовсім оковирних (для знаючих людей) величин.

-

maksim2020

Member

- Откуда: Sunshine State

Але як тоді при тому ж розмірі транзистора їх стає геометрично більше на тій само площині кристала? Sandy Bridge мав ~1 мільярд транзисторів, Raptor Lake вже має 12 мільярдів. Як, без фізичного зменшення розмірів, їх усі розмістити на умовних 250 mm2?EvhenS: ↑ 04.11.2024 14:32 KimRomik

Колись читав що реальний розмір транзистора так і залишився в районі 30-45нм. Там тунельні ефекти і інші телепорти електронів по ізолятору не дають зробити робочий пристрій. Просто примудряються пакувати транзистори плотніше, а для цього треба якось новий процес називати щоб було видно що він кращий. Тому маркетингові нанометри зменшилися до зовсім оковирних (для знаючих людей) величин.

-

the lamer

Member

12 мільярдів транзисторів на 250 кв. - Це розмір майданчика під один транзистор: 150х150нм. Є ще куди ущільнювати транзистори розміром близько 30х60нм, чи не так?maksim2020: ↑ 04.11.2024 15:08Але як тоді при тому ж розмірі транзистора їх стає геометрично більше на тій само площині кристала? Sandy Bridge мав ~1 мільярд транзисторів, Raptor Lake вже має 12 мільярдів. Як, без фізичного зменшення розмірів, їх усі розмістити на умовних 250 mm2?EvhenS: ↑ 04.11.2024 14:32 KimRomik

Колись читав що реальний розмір транзистора так і залишився в районі 30-45нм. Там тунельні ефекти і інші телепорти електронів по ізолятору не дають зробити робочий пристрій. Просто примудряються пакувати транзистори плотніше, а для цього треба якось новий процес називати щоб було видно що він кращий. Тому маркетингові нанометри зменшилися до зовсім оковирних (для знаючих людей) величин.

-

EvhenS

Member

- Откуда: Черкаси

maksim2020 розміри транзисторів потихеньку зменшуються, але педівікія каже що у 3нм транзисторів розмір затвору 40-50нм.

https://en.wikipedia.org/wiki/3_nm_proc ... te-IRDS-12

Тобто у 10А реальних ангстрем буде десь 200-250.

https://en.wikipedia.org/wiki/3_nm_proc ... te-IRDS-12

Тобто у 10А реальних ангстрем буде десь 200-250.

-

Scoffer

Member

maksim2020

Як-як, спочатку на одне ребро поставили, потім на інше, отак і живемо Ну і розміри поки що дійсно трішки зменшуються, але вже не в рази.

Ну і розміри поки що дійсно трішки зменшуються, але вже не в рази.

Якщо повернути старий-добрий планарний техпроцес і старі ж стандарти вимірювання, то ми зараз були б десь на 12-14 нанометрах приблизно за тими мірками.

Як-як, спочатку на одне ребро поставили, потім на інше, отак і живемо

Якщо повернути старий-добрий планарний техпроцес і старі ж стандарти вимірювання, то ми зараз були б десь на 12-14 нанометрах приблизно за тими мірками.

-

taras_cs

Member

- Откуда: Варшава-Київ-Дніпро

Ми на роботі якось докупили планки пам'яті тієї самої серії та об'єму, але вироблені пізніше. Це була пам'ять DDR3 Goodram.

Жодних радіаторів на ній не було, тому будо чудово видно, що чіпи на новіших планках були відчутно менші (при тій самій кількості).

Жодних радіаторів на ній не було, тому будо чудово видно, що чіпи на новіших планках були відчутно менші (при тій самій кількості).

-

MetalistForever

Member

- Откуда: Харьков

Старая картинкаScoffer: ↑ 04.11.2024 16:28 maksim2020

Як-як, спочатку на одне ребро поставили, потім на інше, отак і живемоНу і розміри поки що дійсно трішки зменшуються, але вже не в рази.

Якщо повернути старий-добрий планарний техпроцес і старі ж стандарти вимірювання, то ми зараз були б десь на 12-14 нанометрах приблизно за тими мірками.

-

vmsolver

Member

Да сколько можно сравнивать топологические нормы с реальными размерами транзисторов? Писал ранее пост оптимизма с табличкой.

Ну и раз залез в поиск отсюда цитата, печатать лениво ))

Ну и раз залез в поиск отсюда цитата, печатать лениво ))

Сейчас техпроцесс просто имеет название в стиле старого привычного упоминания какого-то размера, только это давно не упоминание реального размера чего-то, а что-то вроде рейтинга, показывающего что-то похожее на то, насколько данный техпроцесс плотнее тех старых, когда размер там имел что-то под собой, причём приблизительно, потому что надо различать как бы "основные" техпроцессы, это как бы новые, базовые, и их улучшения, вот для основных рейтинг ещё кое как приблизительно работает, но со временем всё хуже, уже всё плохо и с этим, а для улучшенных там уже просто уменьшается число и какое получается так и называют, это уже просто маркетинг.

То ничего бы уже не работало, токи утечки съедали бы всё питание. В своё время п/п индустрия подзастряла на 28 нм из-за этого, а дальнейший прогресс начался строго после отказа от планарных транзисторов в пользу плавниковых (FinFET), которые вот-вот тоже будут заменены на All around gate типы.Scoffer: ↑ 04.11.2024 16:28Якщо повернути старий-добрий планарний техпроцес і старі ж стандарти вимірювання, то ми зараз були б десь на 12-14 нанометрах приблизно за тими мірками.

-

Keyser Soze

Member

Новые станки для печатания денег  Все их хотят заполучить.

Все их хотят заполучить.

-

Scoffer

Member

vmsolver

Ні, планарна топологія не обмежена 28 нанометрами. На 20нм оракл свої проци клепав, поки ще клепав, і на тих же 20нм оператива робиться, самс тільки обіцяє 14нм і знову ж таки планарних. На 28 сиділи тому ж чому і на 14фінфеті - зручненько бабоси стригти.

Відправлено через 2 хвилини 56 секунд:

І так, фінфет трішки економічніший, але одночасно і менш частотний. Що ринок просить, те і отримує.

Ні, планарна топологія не обмежена 28 нанометрами. На 20нм оракл свої проци клепав, поки ще клепав, і на тих же 20нм оператива робиться, самс тільки обіцяє 14нм і знову ж таки планарних. На 28 сиділи тому ж чому і на 14фінфеті - зручненько бабоси стригти.

Відправлено через 2 хвилини 56 секунд:

І так, фінфет трішки економічніший, але одночасно і менш частотний. Що ринок просить, те і отримує.

-

KimRomik

Member

тобто це одна з причин деградації 13900K/14900K, так?vmsolver: ↑ 04.11.2024 17:17 То ничего бы уже не работало, токи утечки съедали бы всё питание.

-

vmsolver

Member

Scoffer

Оракл может и клепал, но то прыжок с подбросом кепки, индустрия на 20нм особо уже ничего не делала, пыталась, но не делала, тогда вышли 22 нм процы от интел на FinFET, потом он перешел на 14нм, а другие производители прыгнули с 28 нм сразу на 14 и 16 нм FinFET, и прыжок этот составил лет 5, а может и больше. И всё из-за токов утечек.

Відправлено через 2 хвилини 54 секунди:

Оракл может и клепал, но то прыжок с подбросом кепки, индустрия на 20нм особо уже ничего не делала, пыталась, но не делала, тогда вышли 22 нм процы от интел на FinFET, потом он перешел на 14нм, а другие производители прыгнули с 28 нм сразу на 14 и 16 нм FinFET, и прыжок этот составил лет 5, а может и больше. И всё из-за токов утечек.

Он другой, зато прогресс пошел дальше, текущие проекты по планарным технологиям не сделать.Scoffer: ↑ 04.11.2024 17:33І так, фінфет трішки економічніший, але одночасно і менш частотний

Відправлено через 2 хвилини 54 секунди:

Нет, токи утечки и любые виды деградации это разные истории.KimRomik: ↑ 04.11.2024 18:04 тобто це одна з причин деградації 13900K/14900K, так?

-

Scoffer

Member

Так може і не треба? Кількість транзисторів в чіпах вже якась захмарна, а приріст продуктивності мізерний.vmsolver: ↑ 04.11.2024 18:17текущие проекты по планарным технологиям не сделать.

Не такий страшний чорт, як його малюють. DRAM поки що вся планарна, хоча здавалось би кого-кого, а її б найбільше мало хвилювати це питання.vmsolver: ↑ 04.11.2024 18:17И всё из-за токов утечек.

-

AssayMAS

Member

- Откуда: ][аркiв

нет тут главное что измеряют - раньше размер транзистора измеряли, сча тех процесс (что часть свойств транзистора). И одинаковые тех процессы с разных заводов могут иметь разный вплоть до +-50% размер транзистора.taras_cs: ↑ 04.11.2024 14:14Тут головне - хто і як рахує

Ранее когда процы были до 1 ГГц совали 1 транзистор, а для повышения ГГц суют ребрёные с плавников - что по сути несколько транзисторов. И они строенные счетверённые уже 3+ГГц могут. там масса мелких улучшений=доп слоёв литографии, что дают по +5%... и через года уже не 3ГГц а 5ГГц.

-

bclogin

Junior

Навіщо вводити в оману читача?Зокрема, за допомогою цього обладнання буде освоєно техпроцес A10 (10 ангстрем), який на два покоління випереджає технологію виробництва 2 нм.

А10 це маркетингова назва, яка не має жодного відношення до 10 ангстрем.

Технологій виробництва "2 нм" теж в природі не існує, є процесс N2 від TSMC

-

KimRomik

Member

чому мізерний?Scoffer: ↑ 04.11.2024 22:53Так може і не треба? Кількість транзисторів в чіпах вже якась захмарна, а приріст продуктивності мізерний.vmsolver: ↑ 04.11.2024 18:17текущие проекты по планарным технологиям не сделать.

продуктивність графічних процесорів росте по геометричній прогресії, і для цього кожні 2 роки збільшують кількість ядер, а разом з ними і транзистори

-

Sanьka

Member

А ще жор проців в 300вт і відях 400-500вт вже не є чимось дивним. Вже від одного параметра відмовились, аби запхати більше. Думаю наступним параметром буде ціна.KimRomik: ↑ 05.11.2024 01:00чому мізерний?Scoffer: ↑ 04.11.2024 22:53

Так може і не треба? Кількість транзисторів в чіпах вже якась захмарна, а приріст продуктивності мізерний.

продуктивність графічних процесорів росте по геометричній прогресії, і для цього кожні 2 роки збільшують кількість ядер, а разом з ними і транзистори

Проци будуть дорожчати , бо кожен новий прогрес все дорожче обходиться.