Пропоную обговорити Lenovo підтвердила січневий реліз мобільних чипів Intel Core 14-го покоління

Цікаво чи буде підтримка AVX-512 ?

Останні статті і огляди

Новини

Lenovo підтвердила січневий реліз мобільних чипів Intel Core 14-го покоління

-

cadet-ua

Member

- Звідки: Ukraine

-

Scoffer

Member

cadet-ua

Ні, не буде, AVX-512 мертвонароджена технологія. В наступних процах буде AVX10, але явно не в рефреші раптор лейка.

Ні, не буде, AVX-512 мертвонароджена технологія. В наступних процах буде AVX10, але явно не в рефреші раптор лейка.

-

cadet-ua

Member

- Звідки: Ukraine

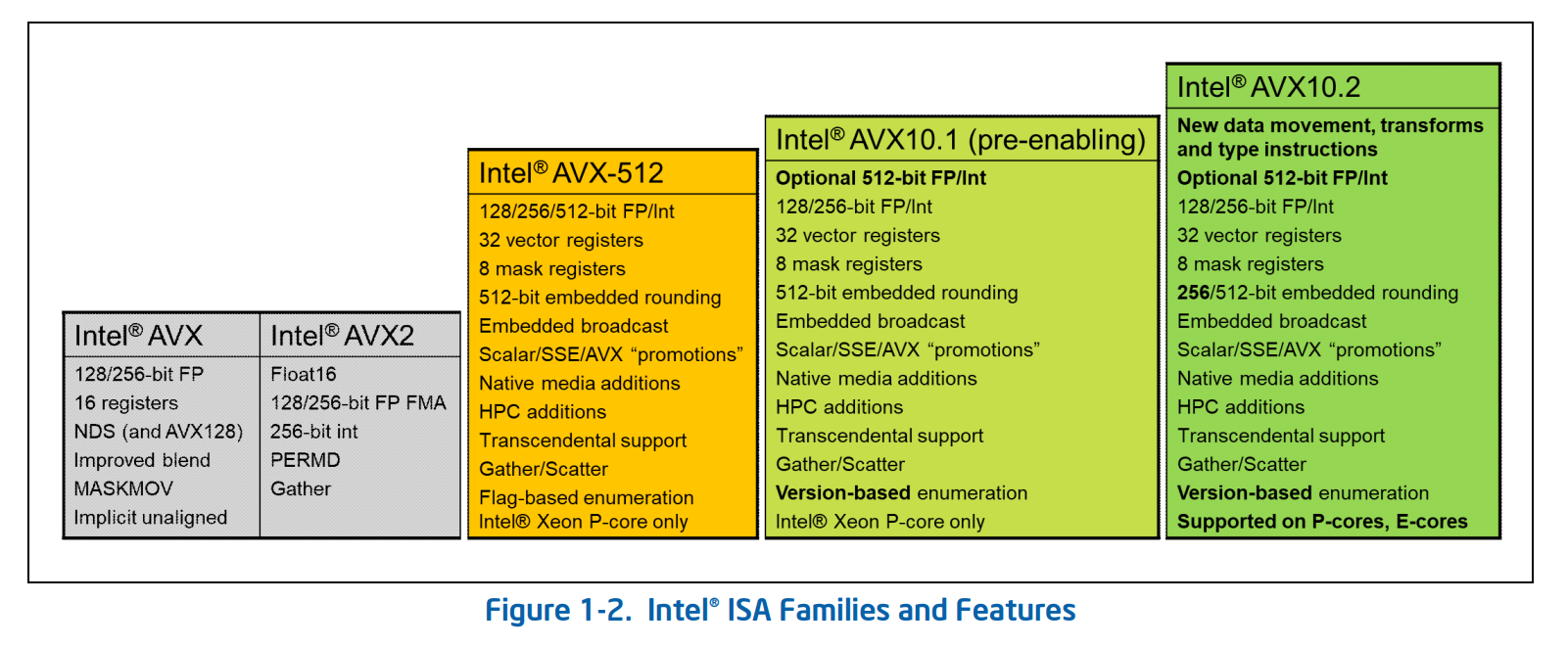

Цікаво, читаючи документ Intel і вивчаючи те, що Intel хоче зробити, схоже на SVD ARM, де у вас може бути набір інструкцій із більшою довжиною вектора, але такий набір інструкцій все одно може працювати на обладнанні із меншою довжиною вектора. Intel робить набір інструкцій AVX512 нормою, додаючи додаткові функції і шари, та перейменовуючи його на AVX10. Але, на відміну від AVX512, AVX10 може виконувати код avx512 на апаратному забезпеченні з довжиною вектора 256 і 128 біт. Реалізація по суті залежить від компілятора та обладнання, вона може бути схожа на подвійне підкачування AMD для реалізації avx512 на Zen4 лише з 256 біт. Векторні реєстри довжини. Таким чином, AVX10 є розвитком AVX512, це буде конвергентна уніфікована ISA, яка працюватиме на всіх майбутніх чіпах Intel із різною довжиною регістрів. Те, як вона працює з регістрами меншої ширини, залежить від компілятора та апаратного забезпечення.Scoffer: ↑ 27.12.2023 09:57 cadet-ua

Ні, не буде, AVX-512 мертвонароджена технологія. В наступних процах буде AVX10, але явно не в рефреші раптор лейка.

Тепер треба шукати що буде пропонуваи AMD з цього приводу...

-

Scoffer

Member

А шо їм пропонувати? Теж реалізують у себе AVX10 в якомусь там майбутньому зені.cadet-ua: ↑ 27.12.2023 11:30Тепер треба шукати що буде пропонуваи AMD з цього приводу

-

ImperiumAeternum

Member

Scoffer

AVX10.1 это просто переименованный AVX512. AVX10.2 это не более чем ужасный способ реализовать все ту же AVX512 на гетерогенных архитектурах.

cadet-ua

AMD ничего не нужно делать, у них нет и не планируется процессоров с двумя разными микроархитектурами.

AVX10 не предусматривает гибкой длины регистров. Он только гарантирует что 512-битные инструкции будут работать на 256-битных FPU. Никаких гарантий касательно 1024 бит не даётся. Поддержки 128-битных FPU тоже нет.

Для сравнения на ARM можно любой вектор от 128 до 2048 бит задать. Вот это гибкая длина векторов, то что предлагает Интел — нет.

AVX10.1 это просто переименованный AVX512. AVX10.2 это не более чем ужасный способ реализовать все ту же AVX512 на гетерогенных архитектурах.

cadet-ua

AMD ничего не нужно делать, у них нет и не планируется процессоров с двумя разными микроархитектурами.

AVX10 не предусматривает гибкой длины регистров. Он только гарантирует что 512-битные инструкции будут работать на 256-битных FPU. Никаких гарантий касательно 1024 бит не даётся. Поддержки 128-битных FPU тоже нет.

Для сравнения на ARM можно любой вектор от 128 до 2048 бит задать. Вот это гибкая длина векторов, то что предлагает Интел — нет.

-

Scoffer

Member

ImperiumAeternum

Ні. AVX10.X, де Х - версія AVX. Буде 1, 2, 3 і так до посиніння.

Кожна з цих AVX10 може бути в варіантах на 128, 256 або 512 біт регістрах.

Тобто в якомусь там атомі це позначатиметься як AVX10.1/128, а в серверній корові як AVX10.1/512.

Щодо того що AVX10, м'яко кажучи, дивно реалізований я згоден, але шо від того зміниться?

Відправлено через 2 хвилини 44 секунди:

Взагалі оці всі векторні розширення в CPU в умовах засилля прискорювачів обчислень не більше ніж рудмент з допотопних часів. Зараз можна було б обмежитись 64-бітним SIMD чисто на заповнення і без того 64-бітних регістрів загального призначення, і на тому більше й не треба.

Ні. AVX10.X, де Х - версія AVX. Буде 1, 2, 3 і так до посиніння.

Кожна з цих AVX10 може бути в варіантах на 128, 256 або 512 біт регістрах.

Тобто в якомусь там атомі це позначатиметься як AVX10.1/128, а в серверній корові як AVX10.1/512.

Щодо того що AVX10, м'яко кажучи, дивно реалізований я згоден, але шо від того зміниться?

Відправлено через 2 хвилини 44 секунди:

І воно там працює неадекватно довго. Можна подивитись на ядра фуджиків для суперкомпів. З голою продуктивністю там все дуже і дуже не дуже.ImperiumAeternum: ↑ 27.12.2023 23:04Для сравнения на ARM можно любой вектор от 128 до 2048 бит задать.

Взагалі оці всі векторні розширення в CPU в умовах засилля прискорювачів обчислень не більше ніж рудмент з допотопних часів. Зараз можна було б обмежитись 64-бітним SIMD чисто на заповнення і без того 64-бітних регістрів загального призначення, і на тому більше й не треба.

-

ImperiumAeternum

Member

Scoffer

Точно. Вообще странная вещь, 128 векторы нафиг не нужны и лишь портят и без того костыльный стандарт. Было бы лучше их на мороз выкинуть и оставить AVX10/256 с двойной подкачкой для 128-битных FPU. AVX 10.1 это таки переименованный AVX512 из Сапфиров, исходя из официальных слайдов. Нас интересует AVX10.2, которых на гетерогенных процессорах сможет работать. Для Arrow Lake могли бы и подтянуть.

Точно. Вообще странная вещь, 128 векторы нафиг не нужны и лишь портят и без того костыльный стандарт. Было бы лучше их на мороз выкинуть и оставить AVX10/256 с двойной подкачкой для 128-битных FPU. AVX 10.1 это таки переименованный AVX512 из Сапфиров, исходя из официальных слайдов. Нас интересует AVX10.2, которых на гетерогенных процессорах сможет работать. Для Arrow Lake могли бы и подтянуть.

- спойлер

-

-

Scoffer

Member

ImperiumAeternum

Та ні, не перейменований. Розширений вниз до 128/256 біт. Ну або даунгрейджений, навивай як хочеш. В найближчих е-ядрах його не буде тому що там фізично потрібні регістри масок, а не тільки загального призначення. А щодо арма, то гнучкість там теж дуже умовна: окрім згаданого мною проца для суперкомпів більше ніякі ядра не вміють в вектори інакші ніж 128-біт, і в осяжному майбутньому вміти не збираються тому що жор, а це не сегмент армів. Власне, інтел скоріш за все теж почали даунгрейдити бітності через жор, інших значимих причин на те не видно.

Та ні, не перейменований. Розширений вниз до 128/256 біт. Ну або даунгрейджений, навивай як хочеш. В найближчих е-ядрах його не буде тому що там фізично потрібні регістри масок, а не тільки загального призначення. А щодо арма, то гнучкість там теж дуже умовна: окрім згаданого мною проца для суперкомпів більше ніякі ядра не вміють в вектори інакші ніж 128-біт, і в осяжному майбутньому вміти не збираються тому що жор, а це не сегмент армів. Власне, інтел скоріш за все теж почали даунгрейдити бітності через жор, інших значимих причин на те не видно.

-

ImperiumAeternum

Member

Scoffer

128 и 256 битные векторы всегда были. Перечитайте слайд.

128 и 256 битные векторы всегда были. Перечитайте слайд.

-

Scoffer

Member

ImperiumAeternum

Всі ранні вестори були 64-бітними. Наприклад MMX, 3dnow і оте все. Потім їх розширили. Але то були часи до прискорювачів обчислень. Зараз все це не треба. Зараз відяха куди більш ефективно може надати флопсів ніж проц з широкими векторами.

Всі ранні вестори були 64-бітними. Наприклад MMX, 3dnow і оте все. Потім їх розширили. Але то були часи до прискорювачів обчислень. Зараз все це не треба. Зараз відяха куди більш ефективно може надати флопсів ніж проц з широкими векторами.

-

ImperiumAeternum

Member

Scoffer

О MMX речи вообще нет. AVX 10.1 — это все те же AVX512 что известны по Сапфирам. 128/256 бит в AVX512 тоже есть.

О MMX речи вообще нет. AVX 10.1 — это все те же AVX512 что известны по Сапфирам. 128/256 бит в AVX512 тоже есть.