Среди тех, кто ещё рассматривает 13 поколение, потиху даже простой Cinebench мигрирует в категорию стресс тестов.AB-Man: ↑ 17.06.2023 19:00 Как то не слишком информативно. Тем более что точкой отчета ранее считался Prime95

Куда там прайм.

Среди тех, кто ещё рассматривает 13 поколение, потиху даже простой Cinebench мигрирует в категорию стресс тестов.AB-Man: ↑ 17.06.2023 19:00 Как то не слишком информативно. Тем более что точкой отчета ранее считался Prime95

Согласен, когда в стоке наваливают 330вт и после андервольта выходит -100вт, без потери производительности...manbearboar: ↑ 17.06.2023 18:58Как бы 230Вт уже после даунвольта - это ещё больший кек, чем 300Вт в номинале.Earanak: ↑ 17.06.2023 18:11 ~235вт выходит в Corona Render 9

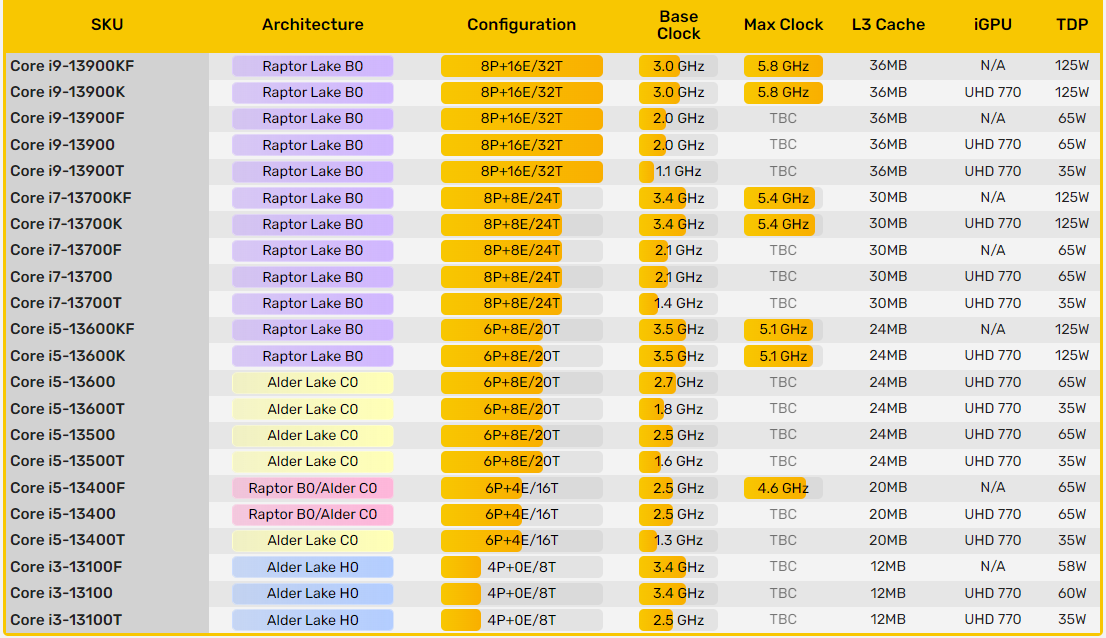

Степинг 13500 Alder Lake C0 прямо говорит о том, что используются под него дефектные 12900 с двумя отключенными Р ядрами.AB-Man: ↑ 17.06.2023 19:06 Потому что i5 Gen 13 это не AlderLake, они лишь имеют у себя внутри часть блоков от AlderLake.

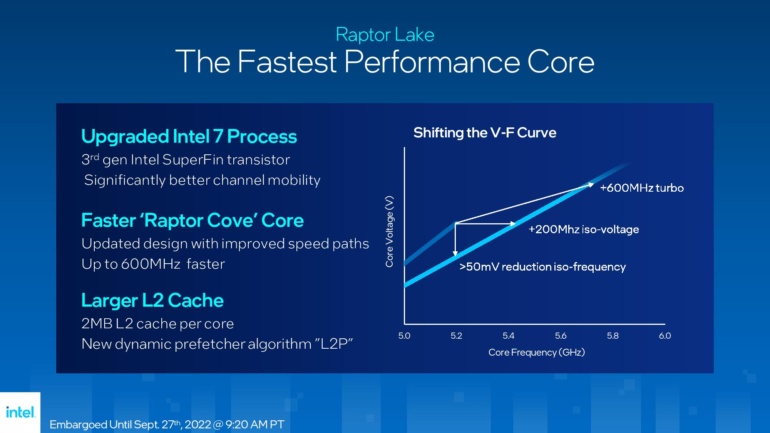

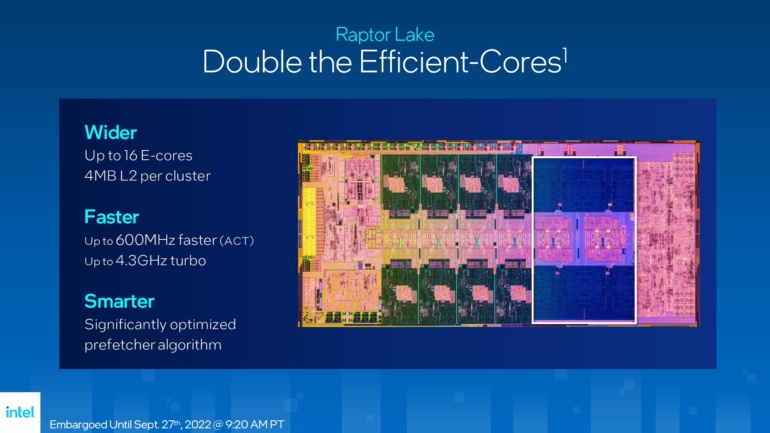

В Raptor Cove, по сравнению с Golden Cove, улучшили структуры памяти и кэша, что улучшило общую эффективность.manbearboar: ↑ 17.06.2023 19:02Тем временем 13400 и 13500 могут жрать хорошо за 100Вт, так как являются перемаркированный альдерами и тех оптимизаций, которые есть у Раптора туда не завезено.+Felix+: ↑ 17.06.2023 18:57 Но вот i3-i5 без К очень даже экономичны

При чём тут 13е если речь о предстоящем 14м? В новом могут обновить архитектуру младших чипов до актуальной - в этом был бы смысл.manbearboar: ↑ 17.06.2023 19:38 +Felix+

13400 на новом кристалле, там кеш будет обрезан до уровня ADL.

Повторяю вопрос: при чём тут 13 поколение? Я про альтернативные спеки этих процов вообще ничего не говорил, это вы их привелиmanbearboar: ↑ 17.06.2023 20:04 +Felix+

Спеки 13400/13500 указаны на ark.intel.com, другими они не могут быть.

Я отвечал на ваше+Felix+: ↑ 17.06.2023 19:50 При чём тут 13е если речь о предстоящем 14м?

Не очень похоже, что это было про 14 поколение.+Felix+: ↑ 17.06.2023 18:57 Но вот i3-i5 без К очень даже экономичны

Но что вы уже отвечали+Felix+: ↑ 17.06.2023 19:29 Если в 14 поколении младшие чипы переведут на Raptor Cove, то они по идее станут еще эффективнее, а точнее, скорее всего, поднимут кеш+частоты при том же уровне TPD

Что значит попадётся, если это уже выпущенный проц с конретными ттх. Неопределённая архитектура ядер пока только у предстоящего поколения, про которое собственно и сабж и ожиданияmanbearboar: ↑ 17.06.2023 19:38 Кеш L2 увеличили, но даже если вам сильно повезёт и попадётся 13400 на новом кристалле, там кеш будет обрезан до уровня ADL.

Немного Л2 кэша дали и все. Это даже на отдельную микроархитектуру не тянет, что сам Интел и подтверждает во всех своих документах+Felix+: ↑ 17.06.2023 19:29 В Raptor Cove, по сравнению с Golden Cove, улучшили структуры памяти и кэша

Возможно увеличение с 1.25 МБ до 2 МБ на ядро потребовало каких-то изменений, но в инженерные дебри не лез, не знаю даже есть ли в публичном доступе какие-то детали на счёт этого, просто взял цитату с одного зарубежного ресурса.ImperiumAeternum: ↑ 18.06.2023 01:21 Про улучшения «структур памяти» не расскажете? Это ещё что за чудо?

Это смотря что вы называете микроархитектурой. Если "глобальную" конфигурацию и структуру - то это одно, а если для этого достаточно улучшенного производственного процесса и оптимизаций, то это другое. Тут очевидно второй вариант, не просто ж так Интел обозвала архитектуру ядер по другому.ImperiumAeternum: ↑ 18.06.2023 01:54 +Felix+

Опять таки никак не относится к микроархитектуре. Что касается инженерных дебрей — такой же IPC как и у Golden Cove, значит это те же самые Golden Cove.

Это и называют микроархитектурой.+Felix+: ↑ 18.06.2023 02:23 Это смотря что вы называете микроархитектурой. Если "глобальную" конфигурацию и структуру - то это одно

А это просто степпинг. Не микроархитектура. И никогда ею не было.+Felix+: ↑ 18.06.2023 02:23 а если для этого достаточно улучшенного производственного процесса и оптимизаций, то это другое

Интересно и действительно могло бы сойти за микроархитектурную разницу. Однако предполагаю, что дело исключительно в оптимизации нагрузки между Е/Р ядрами. А микрокод — не микроархитектура.Ну и IPC архитектур не совсем идентичные.

Говорят что при DDR5-4800 IPC у P-ядер на 2-3% выше, а E-ядер на 6-7%, хотя в целом примерно схоже с "золотой бухтой".