vmsolver

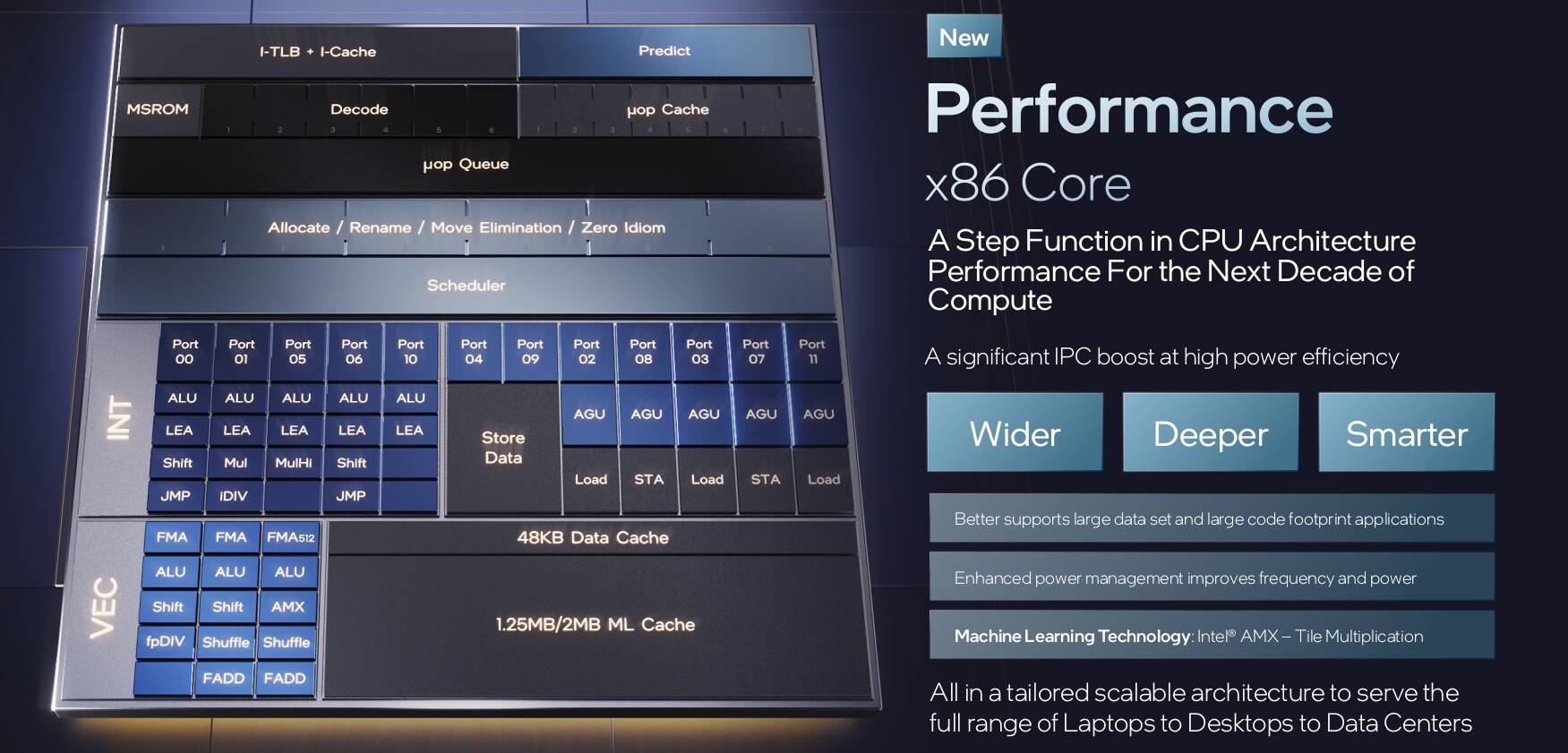

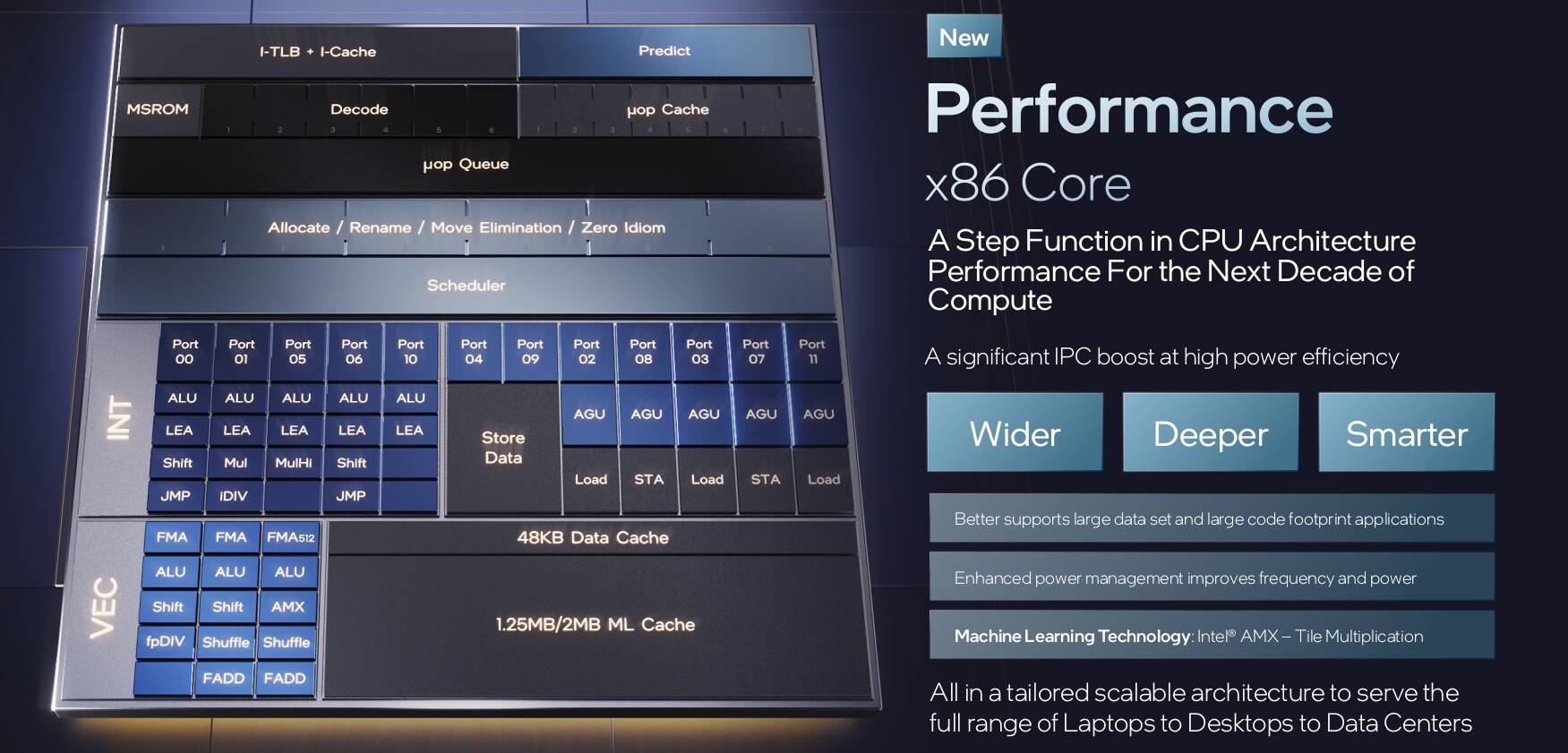

Слайд от Интел с FMA512.

- спойлер

-

https://www.anandtech.com/show/16881/a- ... tectures/5

Дата новости, что AVX-512 таки не будет это

19 августа 2021 года.

До этого Интел всячески мяли титьки и не признавались, как оно будет. На профильных форумах ходили споры о том как Интел собирается заставить это работать, заявляя avx-512 в P-core и не запилив его в E-core.

Финальный ответ - тупо никак.

Відправлено через 6 хвилин 9 секунд:

А вы почитайте его описание, найдите там упоминание что он "детектирует использование потоком тяжёлых инструкций и сигнализирует об этом оси" и сложите два плюс два.

В итоге идея редуцировала в пару строчек в коде W11, который "неприоритетные" потоки запихивает на e-ядра.

Что характерно, в августе они уже говорили что отключат авх512 аппаратно

The biggest thing that gets the cut is that Intel is losing AVX-512 support inside Alder Lake. When we say losing support, we mean that the AVX-512 is going to be physically fused off, so even if you ran the processor with the E-cores disabled at boot time, AVX-512 is still disabled

https://www.tomshardware.com/news/how-t ... ve-avx-512

Но на релизе оказалось, что на части процев его можно включить, потому что более ранние партии выпускались без аппаратной блокировки.

По датам выпуска этих партий можно судить когда внутри Интел ещё зиждилась надежда, что thread director в паре с W11 всё разрулит.

Відправлено через 13 хвилин 32 секунди:

Физически существующие доказательства дрыганий - это партии продажных Альдеров с живым AVX512 блоком.

Это не инженерники, уже финальная версия.

To check for AVX-512 compatibility, Zingaburga says you'll need to check the batch number on your Alder Lake CPU or the chip you are potentially buying. Batch numbers with V149 or X149 or lower will have the AVX-512 instruction set enabled on the silicon. While codes starting with V150 or X150 through V201 or X201 could potentially support AVX-512, it's not guaranteed.

А такую драматичную драму как вы могли пропустить?

In short, early production units of Alder Lake chips had their AVX-512 instruction sets intact from the factory, but Intel didn't want it enabled for unknown reasons. Motherboard manufacturer's caught wind of this and created a switch to allow AVX-512 right from the BIOS.

Intel countered this with new microcode updates to stop AVX-512 enablement, but even that was countered by the fact that older BIOS microcodes still existed, and users could switch to those versions at any time.