На одному CCX* У чіплеті загалом, буде так само 32МБ, проте розподілені на 16 ядер, а не 8Щоправда, для цього AMD довелося вдвічі урізати обсяг кеш-пам'яті третього рівня: з 32 до 16 Мбайт в одному чиплеті.

Последние статьи и обзоры

Новости

Серверні процесори AMD EPYC Bergamo використовують 16-ядерні чіплети Zen 4c

-

Denvys5

Member

- Откуда: Kyiv

Пропоную обговорити Серверні процесори AMD EPYC Bergamo використовують 16-ядерні чіплети Zen 4c

-

manbearboar

Member

При размере 1.4мм2 такое ужатое 4с ядро меньше одного Е-ядра, которое 1.7мм2.

При этом сохранен HT и поддержка AVX512.

При этом сохранен HT и поддержка AVX512.

-

VRoman

Member

- Откуда: Albuquerque, NM, USA

И даже L1 и L2 не урезали, а только L3. Наверное оптимизировали под VCache. Буст значительно снизился, но ядер вдвое больше. Энергоэффективность должна достигнуть новых высот.

-

Scoffer

Member

manbearboar

Ти прям як маркетолог. Оце б ще порівнювати 10нм з 5 по площі і зненацька виявити що 5 таки менше.

Ти прям як маркетолог. Оце б ще порівнювати 10нм з 5 по площі і зненацька виявити що 5 таки менше.

-

ronemun

Advanced Member

Scoffer

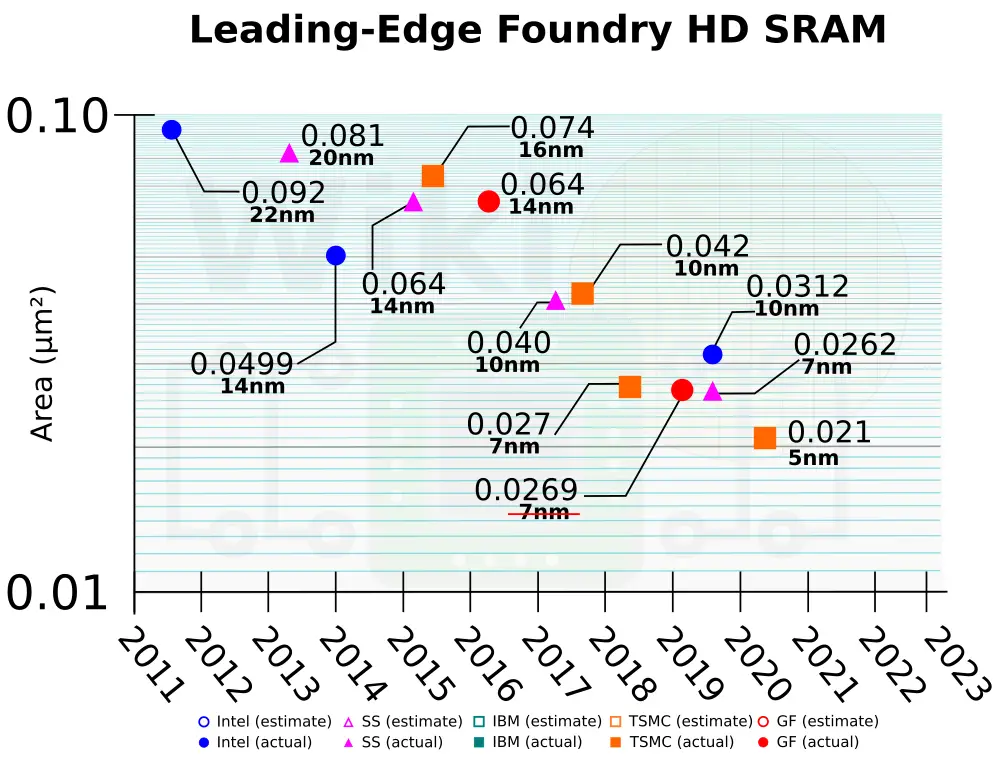

в Інтела SRAM займає точну туж площу що і в АМД на 5 нм - 1 МБайт/0,5мм2

В цьому якраз дивовижна нерозторопність Інтела що вони могли б за ніщо напхати того кешу і перегнати АМД з їх 3D на порядки

зарашній 13900 має всього 36 МБайт L3 кешу. Інтелу хватило б додати всього 42 мм2 до зарашніх 255 щоб забезпечити 120 МБ єдиного суцільного кешу, 12 банок по 10 МБ, не рахуючи 32 МБ L2, при цьому заткнула б АМД в іграх назавжди. Натомість вона витягує останні соки розганяючи частоту і споживання, і третину кристалу займають безпотрібна убога відяха, медіакодер і відеопорти, і все одно програє АМД з 3д кешом

на тому ж сайті semianalysis є аналіз зарашніх 60 ядерних і наступних 66 ядерних Xeon. Тут Інтел все таки щось догадалась і в наступних Xeon збільшить L3 блоки з 1,4 до 5МБ, а також кеші снуп і мережі даних. Але от ядро з 2 МБ L2 кешу займає 9,3 мм2, і це після 10+ оптимізацій. Зате свій дешевий техпроцес. В АМД зараз ядро майже в 4 рази меньше, хоча кеш L2 всього 1МБ, у 2 рази слабший FPU і немає прискорювачів AMX і DLB/DSA/IAA/QAT. Зате є в 2 рази більше ядер, економність, маленькі кристали і в 1,5 рази меньша площа кремнію. З другої сторони навіщо такі малі кристали в АМД якщо вона спокійно може їх всі обєднати на площі в 500 мм2, або розбити по 64 ядра, і при цьому буде майже спільний кеш і значно швидший доступ до IODie?

в Інтела SRAM займає точну туж площу що і в АМД на 5 нм - 1 МБайт/0,5мм2

В цьому якраз дивовижна нерозторопність Інтела що вони могли б за ніщо напхати того кешу і перегнати АМД з їх 3D на порядки

зарашній 13900 має всього 36 МБайт L3 кешу. Інтелу хватило б додати всього 42 мм2 до зарашніх 255 щоб забезпечити 120 МБ єдиного суцільного кешу, 12 банок по 10 МБ, не рахуючи 32 МБ L2, при цьому заткнула б АМД в іграх назавжди. Натомість вона витягує останні соки розганяючи частоту і споживання, і третину кристалу займають безпотрібна убога відяха, медіакодер і відеопорти, і все одно програє АМД з 3д кешом

на тому ж сайті semianalysis є аналіз зарашніх 60 ядерних і наступних 66 ядерних Xeon. Тут Інтел все таки щось догадалась і в наступних Xeon збільшить L3 блоки з 1,4 до 5МБ, а також кеші снуп і мережі даних. Але от ядро з 2 МБ L2 кешу займає 9,3 мм2, і це після 10+ оптимізацій. Зате свій дешевий техпроцес. В АМД зараз ядро майже в 4 рази меньше, хоча кеш L2 всього 1МБ, у 2 рази слабший FPU і немає прискорювачів AMX і DLB/DSA/IAA/QAT. Зате є в 2 рази більше ядер, економність, маленькі кристали і в 1,5 рази меньша площа кремнію. З другої сторони навіщо такі малі кристали в АМД якщо вона спокійно може їх всі обєднати на площі в 500 мм2, або розбити по 64 ядра, і при цьому буде майже спільний кеш і значно швидший доступ до IODie?

-

manbearboar

Member

Они уже и так без штанов остались, пытаясь конкурировать 257мм2 кристаллом с мелкими райзенами.ronemun: ↑ 08.06.2023 03:43 могли б за ніщо напхати того кешу і перегнати АМД

-

Scoffer

Member

ronemun

- спойлер

-

Cirax

Member

- Откуда: Киев

Там маркетинговые размеры, не имеющие ничего общего с реальностью.Scoffer: ↑ 07.06.2023 23:42 manbearboar

Ти прям як маркетолог. Оце б ще порівнювати 10нм з 5 по площі і зненацька виявити що 5 таки менше.

10 и 5 на практике могут и не отличаться по занимаемой площади.

-

Scoffer

Member

Cirax

Вище картинка. Відрізняються в півтора рази.

Відправлено через 8 хвилин 13 секунд:

І це на самому щільному елементі, SRAM. Самі ядра, як правило, розщільнюють заради частот.

Вище картинка. Відрізняються в півтора рази.

Відправлено через 8 хвилин 13 секунд:

І це на самому щільному елементі, SRAM. Самі ядра, як правило, розщільнюють заради частот.

-

ronemun

Advanced Member

Scoffer

є ж прямі фотки кристалів Раптора навіть на 200 мегапікселів, з точністю розмірів кристалу до 1 мкм, все легко можна вирахувати. Там же є фотки кристалу Райзена 7600, і в статті табличка показує що 1МБ кешу L2 займає 0,49мм2 в zen4 s zen4c

Враховуючи що площа кешів і іншх регулярних структур в АМД займає 80% кристалу Zen4, і трохи менше в Zen4c, то в Інтела єдиний козир нарощувати кеші і т.п.

Також Інтел легко робить дешеві 750 мм2 кристали, що дозволяє робити кеш і ядра одним блоком, що важливо для серверів з їх рівномірністю доступу, і не бавлячись з чіплетами

Ще замітно, в Інтела інтерфейси DDR5 займають значно меньшу площу, при тому витримуютть вищу частоту і кількість ранків. Навіщо тоді робити мало каналів? всього 8 на 60 ядер це глупо, тим більше в серверах і процах з підтримкою потужного FPU/AI де колосальне навантаження на оперативу

Звичайно, Інтелу зробити чіп на 250 мм2 взагалі нічого не коштує, в них свої заводи, вони навіть 750 мм2 кристали майже без браку ліплять зараз

Але Інтел чомусь запхала стару недовідяху, яка з кодеками і виходами займає 55мм2, хоча вже мали готові окремі копійчані кристали значно кращої і економічної по площі архітектури Xe. Спільно з процом на підкладці причепи до неї 1 чіп LPDDR5 на 3 Гбайт і радості від інтеграшки на порядок більше.

А ще врахувати скільки проців йде з відключеною відеокартою, або її не використовують тому що є десктопна - то витрати дорогоцінного техпроцесу на недовідяхи явно зашкалюють

є ж прямі фотки кристалів Раптора навіть на 200 мегапікселів, з точністю розмірів кристалу до 1 мкм, все легко можна вирахувати. Там же є фотки кристалу Райзена 7600, і в статті табличка показує що 1МБ кешу L2 займає 0,49мм2 в zen4 s zen4c

Враховуючи що площа кешів і іншх регулярних структур в АМД займає 80% кристалу Zen4, і трохи менше в Zen4c, то в Інтела єдиний козир нарощувати кеші і т.п.

Також Інтел легко робить дешеві 750 мм2 кристали, що дозволяє робити кеш і ядра одним блоком, що важливо для серверів з їх рівномірністю доступу, і не бавлячись з чіплетами

Ще замітно, в Інтела інтерфейси DDR5 займають значно меньшу площу, при тому витримуютть вищу частоту і кількість ранків. Навіщо тоді робити мало каналів? всього 8 на 60 ядер це глупо, тим більше в серверах і процах з підтримкою потужного FPU/AI де колосальне навантаження на оперативу

які мєлкі райзени? 2 чіплети по 58мм2 і один хаб на 127 = 243. Це хіба сильно меньше? А відчуваєте різницю в ціні кристалів на 5 і 6нм в TSMC і 10/7 нм у Інтел. І їх ще надійно спаяти треба. І все одно це всього 32 МБ свого кешу, тоді як в Інтел 36, + L2 в 2 рази більший, що значно зменшує залежність ядер від ненажерливих сусідів. АМД спасає лише 3д кеш, і то лише на один чіплет, і який ще тре окремо зробити і прикріпити через всі 10 000 отворів, не змарнувавши обидва кристали.manbearboar: ↑ 08.06.2023 08:27Они уже и так без штанов остались, пытаясь конкурировать 257мм2 кристаллом с мелкими райзенами.ronemun: ↑ 08.06.2023 03:43 могли б за ніщо напхати того кешу і перегнати АМД

Звичайно, Інтелу зробити чіп на 250 мм2 взагалі нічого не коштує, в них свої заводи, вони навіть 750 мм2 кристали майже без браку ліплять зараз

Але Інтел чомусь запхала стару недовідяху, яка з кодеками і виходами займає 55мм2, хоча вже мали готові окремі копійчані кристали значно кращої і економічної по площі архітектури Xe. Спільно з процом на підкладці причепи до неї 1 чіп LPDDR5 на 3 Гбайт і радості від інтеграшки на порядок більше.

А ще врахувати скільки проців йде з відключеною відеокартою, або її не використовують тому що є десктопна - то витрати дорогоцінного техпроцесу на недовідяхи явно зашкалюють

-

Scoffer

Member

ronemun

Площу ти можеш вирахувати хоч до нанометра, але кількість транзисторів на душу проца інтел сто років як не публікує. Останнім, здається, бродвел був, чи взагалі хасвел. Тому сама достовірна інфа це з маркетингових матеріалів про щільність.

А ще було б дуже дивно якби інтел 10нм відповідав щільності тсмц 5нм і при цьому не був названий інтел 5нм. У маркетологів масовий інфаркт виникнув би.

Площу ти можеш вирахувати хоч до нанометра, але кількість транзисторів на душу проца інтел сто років як не публікує. Останнім, здається, бродвел був, чи взагалі хасвел. Тому сама достовірна інфа це з маркетингових матеріалів про щільність.

А ще було б дуже дивно якби інтел 10нм відповідав щільності тсмц 5нм і при цьому не був названий інтел 5нм. У маркетологів масовий інфаркт виникнув би.

-

manbearboar

Member

6нм скорее всего заметно дешевле 10нм Интел, потому что те используют четырёхкратное экспонирование на старых DUV станках, а TSMC прожигает самых тонких 4 слоя с помощью EUV, скорее всего в 1 проход.ronemun: ↑ 09.06.2023 04:33 які мєлкі райзени? 2 чіплети по 58мм2 і один хаб на 127 = 243. Це хіба сильно меньше? А відчуваєте різницю в ціні кристалів на 5 і 6нм в TSMC і 10/7 нм у Інтел.

По более ранним слухам 10нм домашних обходятся Интел дороже, чем 7нм контрактникам TSMC, что в принципе ожидаемо.Meanwhile, TSMC's 6nm FinFET (N6) technology successfully completed product yield verification in 2019. Thanks to the reduction in mask layer and the process complexity achieved through EUV lithography technology, N6 technology could achieve better yield and shorter production cycles compared to N7 technology in the manufacture of the same products.

У 7800X3D только 66мм2 на N5, а продаётся он за 450$.

-

ronemun

Advanced Member

Scoffer

Ми ж говоримо про SRAM, однакового обєму, отже і транзисторів. Стандартна комірка SRAM має 8 транзисторів, і це всім відомо. Є ще варіант на 6 транзисторів, які якраз зараз АМД впровадила в Zen4c, але вони були гірші, лише зараз TSMC їх змогла зрівняти з 8 транзисторними

SRAM це кеші L1/2/3, теги, мікрокод, буфери шин даних, і т.п. На фото видно що це половина ядра, я вже мовчу про кеші де її більше 3/4

Очевидно, що в Інтел 7 і в TSMC 5-6-7 нм однакова густина транзисторів для SRAM/регістрових файлів, але ядро проца це маса функціональних блоків, які сильно залежать від конструкції і ефективного розміщення мікроблоків, що в Інтела зовсім слабо, крім деяких блоків, типу інтерфейсів DRAM. Та навіть у АМД, як видно, в Zen4c в 1,5 рази краще вийшло, порівняно з Zen4. Але без кешів/буферів/шин/контролерів памяті і PCIe і т.п. ядра нічого не варті, тож в Інтел ще є шанс догнати АМД на нових техроцесах

2. Генеральний директор Intel, 07.2021: У міру того, як обсяги 10-нанометрових пластин зростають, економічні показники покращуються: вартість 10-нанометрових пластин на 45% нижча в порівнянні з минулим роком.

Своє виробництво завжди дешевшає з часом, а коли окупиться то взагалі безплатне, тоді як TSMC лише піднімає ціни з року в рік настільки що навіть Apple закази зрізала

Якщо придивитись, то в Інтел варіантів кристалів взагалі захмарна, і ще степінгів купа, очевидно, якщо б це було дорого робили б як АМД, пару кристалів на все

3. У 7800X3D 66 мм2 на N5 які нічого не варті без 125+32 на 6нм. Звичайно, це дійсно не дорого, але чомусь ціни на нові десктопні проци АМД такі що втрачає ринок, повністю ігнорує найпоширеніші 2-4 ядерні платформи, нові APU робить на 6нм та й закази в TSMC обрізала сильно, хоч могла б ринок захоплювати дешевими процами - маски ж то вже готові, я вже мовчу розробка вже давно пройшла - тільки друкуй і все. При тому що 16 ядер значно вигідніші ніж 8 - адже досить тільки один кристал на 66 мм2 добавити, а націнка в 250 доларів, майже як у 7800х. А про 3д взагалі мовчу - надбавка 150+ доларів за кристал 32 мм2

Ми ж говоримо про SRAM, однакового обєму, отже і транзисторів. Стандартна комірка SRAM має 8 транзисторів, і це всім відомо. Є ще варіант на 6 транзисторів, які якраз зараз АМД впровадила в Zen4c, але вони були гірші, лише зараз TSMC їх змогла зрівняти з 8 транзисторними

SRAM це кеші L1/2/3, теги, мікрокод, буфери шин даних, і т.п. На фото видно що це половина ядра, я вже мовчу про кеші де її більше 3/4

Очевидно, що в Інтел 7 і в TSMC 5-6-7 нм однакова густина транзисторів для SRAM/регістрових файлів, але ядро проца це маса функціональних блоків, які сильно залежать від конструкції і ефективного розміщення мікроблоків, що в Інтела зовсім слабо, крім деяких блоків, типу інтерфейсів DRAM. Та навіть у АМД, як видно, в Zen4c в 1,5 рази краще вийшло, порівняно з Zen4. Але без кешів/буферів/шин/контролерів памяті і PCIe і т.п. ядра нічого не варті, тож в Інтел ще є шанс догнати АМД на нових техроцесах

1. якщо меньша кількість масок важлива то чому в TSMC ціна на 5нм EUV 17к за пластину, а старий DUV 7нм - 9.3к, 10 нм - 6к, 12нм - 4кmanbearboar: ↑ 09.06.2023 12:37

6нм скорее всего заметно дешевле 10нм Интел, потому что те используют четырёхкратное экспонирование на старых DUV станках, а TSMC прожигает самых тонких 4 слоя с помощью EUV, скорее всего в 1 проход.По более ранним слухам 10нм домашних обходятся Интел дороже, чем 7нм контрактникам TSMC, что в принципе ожидаемо.Meanwhile, TSMC's 6nm FinFET (N6) technology successfully completed product yield verification in 2019. Thanks to the reduction in mask layer and the process complexity achieved through EUV lithography technology, N6 technology could achieve better yield and shorter production cycles compared to N7 technology in the manufacture of the same products.

У 7800X3D только 66мм2 на N5, а продаётся он за 450$.

2. Генеральний директор Intel, 07.2021: У міру того, як обсяги 10-нанометрових пластин зростають, економічні показники покращуються: вартість 10-нанометрових пластин на 45% нижча в порівнянні з минулим роком.

Своє виробництво завжди дешевшає з часом, а коли окупиться то взагалі безплатне, тоді як TSMC лише піднімає ціни з року в рік настільки що навіть Apple закази зрізала

Якщо придивитись, то в Інтел варіантів кристалів взагалі захмарна, і ще степінгів купа, очевидно, якщо б це було дорого робили б як АМД, пару кристалів на все

3. У 7800X3D 66 мм2 на N5 які нічого не варті без 125+32 на 6нм. Звичайно, це дійсно не дорого, але чомусь ціни на нові десктопні проци АМД такі що втрачає ринок, повністю ігнорує найпоширеніші 2-4 ядерні платформи, нові APU робить на 6нм та й закази в TSMC обрізала сильно, хоч могла б ринок захоплювати дешевими процами - маски ж то вже готові, я вже мовчу розробка вже давно пройшла - тільки друкуй і все. При тому що 16 ядер значно вигідніші ніж 8 - адже досить тільки один кристал на 66 мм2 добавити, а націнка в 250 доларів, майже як у 7800х. А про 3д взагалі мовчу - надбавка 150+ доларів за кристал 32 мм2

-

Scoffer

Member

ronemun

Вся твоя гарна теорія рушиться рівно на тому моменті що кеш не є просто голою монолітною SRAM-пам'ятю. Окрім даних, там ще знаходяться і теги з індексами пошуку по даним, і їхня структура для різних архітектур кешів ой яка різна. Плюс всі сучасні кеші набираються зі шматочків і саме по собі забезпечення індексування шматочків теж сильно залежить від структури кешу

Вся твоя гарна теорія рушиться рівно на тому моменті що кеш не є просто голою монолітною SRAM-пам'ятю. Окрім даних, там ще знаходяться і теги з індексами пошуку по даним, і їхня структура для різних архітектур кешів ой яка різна. Плюс всі сучасні кеші набираються зі шматочків і саме по собі забезпечення індексування шматочків теж сильно залежить від структури кешу

-

manbearboar

Member

Это было до того как они осознали своё положение.ronemun: ↑ 09.06.2023 21:37 Якщо придивитись, то в Інтел варіантів кристалів взагалі захмарна, і ще степінгів купа

С тех пор кучу проектов поотменяли.

Видеокарты они заказывают у ТСМЦ, а не пекут на своём бесплатном оборудовании.

При чём именно на 6нм сейчас.

Чиплеты для Метеора и Arrow тоже ТСМЦ будет делать.

Мобильный Arrow вообще полностью TSMC.

Контрактник может окупать оборудование дольше, потому что у них есть заказчики на тот период, когда техпроцесс перестал быть передовым.

Відправлено через 3 хвилини 10 секунд:

5нм немного дороже, потому что больше EUV слоёв использует.ronemun: ↑ 09.06.2023 21:37 то чому ціна на 5нм EUV 17к за пластину, а старий DUV 7нм - 9.3к, 10 нм - 6к, 12нм - 4к

И потому что купят за 17к

-

ronemun

Advanced Member

Scoffer

так, і як видно на фото кристалу раптора теги там взагалі копійки займають - що L3 кешу, що L2. І як видно по фотках 3д кешу L3 в АМД SRAM займає майже всю площу. Тож збільшити кеш L3 в 3 рази Інтелу нічого не коштувало. Заодно кристал став би ширшим, сторони більш рівні, а тоді їх більше вміщається на пластину

так, і як видно на фото кристалу раптора теги там взагалі копійки займають - що L3 кешу, що L2. І як видно по фотках 3д кешу L3 в АМД SRAM займає майже всю площу. Тож збільшити кеш L3 в 3 рази Інтелу нічого не коштувало. Заодно кристал став би ширшим, сторони більш рівні, а тоді їх більше вміщається на пластину