jorg: ↑ 08.08.2022 14:28Особлива грета свою пісеньку під дудку свр вже відспівала та успішно змитаdead_rat: ↑ 08.08.2022 14:22 Можна версію з афтографом Грети Тунберг на кришці?

Два раза прочитал, пока не понял, что речь идёт про песню.

jorg: ↑ 08.08.2022 14:28Особлива грета свою пісеньку під дудку свр вже відспівала та успішно змитаdead_rat: ↑ 08.08.2022 14:22 Можна версію з афтографом Грети Тунберг на кришці?

swan song мабуть.

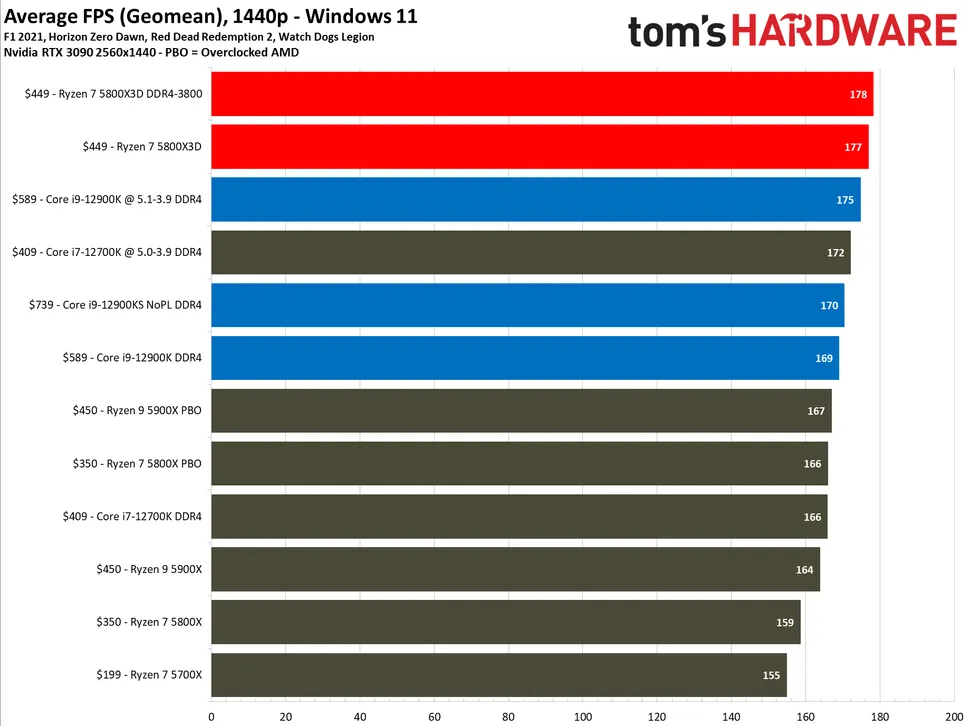

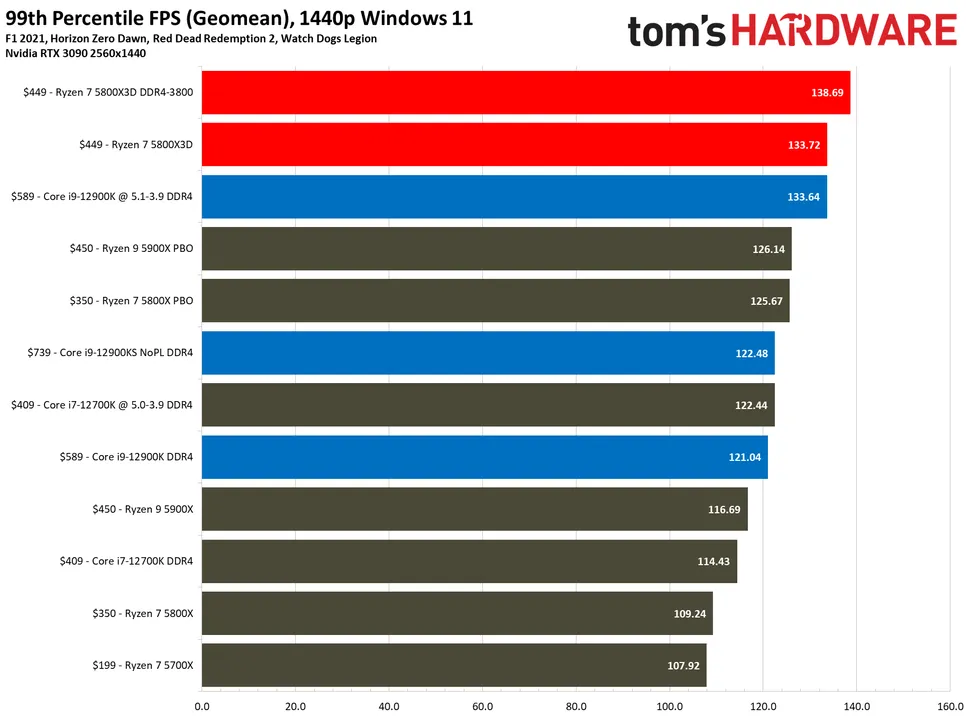

Т.е. вы одному процу одного производителя противопоставляете 2 разных от другого? Интересный подход, не встречал таких.IInLight: ↑ 09.08.2022 04:02Наверняка же конкуренции никакой, правда?

Интел якобы универсальней, и поиграть норм и поработать, но это не так, многозадачность хромаетWWQ: ↑ 09.08.2022 10:28Т.е. вы одному процу противопоставляет 2 разных? Интересный подход, не встречал таких

Вот именно, 12900к под рендеринг, отдельно машина под ютубчик/интернетWWQ: ↑ 09.08.2022 10:282 машины собирать или камни перетыкать в зависимости от задач?

Открою для тебя "тайну", про то, что ТЭЦ в первую очередь спроектированы вырабатывать электричество, а отборы части уже отработавшего на первых ступенях турбины пара для теплообменников отопления и гороячего водоснабжения лишь один из способов увеличения общего КПД электростанцииAlexiy: ↑ 08.08.2022 20:13 Хороший проц, чтобы греться зимой, когда русня развалит ТЭЦ. Знать бы только, что будет электричество)

"Устаревший" это почти синоним обкатанный. Какие там нестабильности?Lorichic: ↑ 09.08.2022 10:51 К середине 2022 уже устаревший проц со старой DDR4, напряжный бэкграунд в плане танцев с дровами и прочих нестабильностей и ненадежностей.

Эти нюансы надеюсь будут решены в новом планировщике процессора, а пока как есть, или рендерим и не трогаем камп или миримся с производительностью мелких ядер в фонеWWQ: ↑ 09.08.2022 12:49"Нюансы" с мелкоядрами нынче решены в В11

так давно це зрозуміло хто очі роззув, а не тільки на частоти і кількість ядер дивиться - все вирішує теплопакет. Два 32 ядерних Epyc по 280 Вт завжди будуть знаачно потужніші за один 64 ядерний з 280 Вт. І завжди проци з високочастотними ядрами коштували знааачно дорожче ніж навіть проци з більшою кількістю ядер тої ж архітектури, але нижчими частотами. Тому якщо тобі тре швидший відгук, а це 80% задач, то вибір очевидний. І ясно що на вищій частоті буде вище і споживання, і в геометричній прогресії. Кому не подобається - не беріть.Lightbuilder: ↑ 09.08.2022 04:38 Ну врешті решт користувачі зрозуміли, що потужність вимірюється у Ваттах. А Інтел швидко пішов на зустріч тім, хто бажає собі потужний комп'ютер! Якщо що, просто жартую.

Яж писав що необхідно було е-ядра в окреме кільце, а основні ядра зі своїм кільцем навпаки мали б меньше станцій, і навіть без системного агента і графіки - їх теж в друге кільце. В Xeon v4 така конструкція давала дуже малі затримки між ядрами, навіть з різних кілець - 45 нс приблизно - а зараз кільця значно швидші. А так виходить що доступ до е-ядер дає приблизно 50 нс, крім тих що всередині четвірки, і то в них під 30. Це і логічніше, полегшує розподіл навантаження при плануванні. А виграш в 12 МБ (4x4-16*0.25) кешу для 13900 досить значний: +33%. В АМД теж кожен чіплет має своє кільце, а потім ІО чіп своїм хабом їх обєднує - і при потребі ядра лізуть в кеш L3 іншого чіплета - він ніби загальний, але віддалений з шаленою затримкою біля 80-120 нс. В Інтела від сили було б 50нс.vmsolver: ↑ 09.08.2022 01:37Е-ядра объединили в 4-ядерный кластер для того, чтобы кольцевая шина была как можно меньше. Ведь если каждое е-ядро имело бы свою станцию, то представьте как быстро бы вырос размер кольца. Считаем у 12900: uncore c КП, 8 ядер, графика, два кластера по 4 ядра, получается 12 станций, а без кластеров было бы: uncore c КП, 8 ядер, графика, 8 е-ядер, итого 18 станций, что много как для десктопа, задержки будут высокие. У 13900 было бы аж 26 станций, что уже за гранью разумного. Значит станции надо экономить, вот и выбрали 4-ядерный кластер для е-ядер, оставив как было ранее во всём остальном.ronemun: ↑ 08.08.2022 23:57Одне не розумію, навіщо було е-ядра обєднувати аж по 4 шт- додаткові затримки, тратити на них стільки повільного кешу л2=4х4=16 мб, який не можна використати іншим ядрам, та ще й приєднувати кожну четвірку в кільце всього через 1ну станцію

Я не удивлюсь, если в будущем, и р-ядра будут соединены, например, по два ядра на станцию. Полосу станции конечно же увеличат, например, в TigerLake уже увеличили в двое.

Два кольца это плохо. Ведь кольцо это не просто шина данных, она системообразующая, она "сшивает" как кеш L3 в единое целое, так и все остальные ресурсы на кристалле. А второе кольцо получается будет прилеплено "с боку" и занимать две станции основного кольца, не садить же 8 е-ядер на одну станцию, вы и от 4 е-ядра на одной станции не в восторге, а что будет при дальнейшем масштабировании? Будет всё хуже и хуже, и не однородно. В общем, текущее решение это меньшее зло.

И ещё раз, кольцо это ещё и "связка" кеша L3 в единое целое, второе кольцо тоже будет с кешем или без? Если с ним, то в системе получится два L3 кеша, что не упрощает систему от слова совсем, тогда (основной)L3 не будет играть роль LLC (Last Level Cashe), а именно для этого он и нужен. А если там второго кеша L3 не будет, то тоже хорошего мало, ведь так или иначе будут увеличенные задержки от е-ядер до L3 и проблемы с полосой к е-ядрам из-за "бутылочного горлышка" между кольцами.

В общем, второе кольцо не нужно, всё усложняется и при этом ничего не улучшается. Тогда уже лучше перейти на сетку, она хотя бы снимает(отодвигает) проблему полосы при масштабировании, но тоже не идеал, и для средних и бюджетных камней оверкилл и вообще не нужна, делать два решения для десктопа Интел скорее всего не захочет. Пока кольцо справляется менять его никто не будет, а схемотехнические трюки ещё даже не начали исчерпываться, поэтому кольцо в десктопе будет ещё долго. Хотя, надо глянуть что даст тайловый дизайн системы в этом плане.

Этот вариант я также рассматривалronemun: ↑ 09.08.2022 23:47 Яж писав що необхідно було е-ядра в окреме кільце,

Как я написал выше, нет, если 8 е-ядер соединить своим кольцом, то эту шину надо как-то соединить с основным, и на это пойдут как минимум две станции как основного так и добавленного. В итоге, что пнём об сову, что совой об пень, только с двумя кольцами сложнее, хуже и дороже. Теперь если е-ядер будет уже 16. Второе кольцо будет уже большое и с высокими задержками из-за размера кольца, полосу шин соединяющие кольца тоже надо увеличить, то есть соединить 4 станции одного кольца с 4-мя станциями другого, а иначе - бутылочное горлышко по полосе, и в любом случае пенальти по задержкам, при многопоточной нагрузке - огромное в случае бутылочного горлышка. А многопоточность, это то ради чего всё это было задумано...ronemun: ↑ 09.08.2022 23:47а основні ядра зі своїм кільцем навпаки мали б меньше станцій,

А на мой взгляд - там им делать нечего, они должны быть в "основной" части процессора, а не в дополнительном огрызке.ronemun: ↑ 09.08.2022 23:47і навіть без системного агента і графіки - їх теж в друге кільце.

У меня нет данных про старые Зионы (мне просто не нужно), но я вижу, что Интел спроектировала гибридную систему так, чтобы кольцо было одно и оно имело наименьшие размеры, при прочих равных это всегда означает наименьшие задержки и отсутствие бутылочных горлышек. Другими словами, то решение, которое Интел реализовала имеет топологические преимущества и вы его ничем не перебьёте, любая более сложная топология будет хуже в плане задержек и определённо будет вызывать беспокойства по поводу масштабирования полосы. Когда я выше писал, что не удивлюсь если на одну станцию повесят два р-ядра, то это именно про это, такое решение позволит упростить топологию соединений и снизить латентность, но и имеет свою цену.ronemun: ↑ 09.08.2022 23:47В Xeon v4 така конструкція давала дуже малі затримки між ядрами, навіть з різних кілець - 45 нс приблизно - а зараз кільця значно швидші. А так виходить що доступ до е-ядер дає приблизно 50 нс, крім тих що всередині четвірки, і то в них під 30. Це і логічніше, полегшує розподіл навантаження при плануванні. В АМД теж виходить кожен чіплет має своє кільце, а потім ІО чіп своїм хабом їх обєднує - і при потребі ядра лізуть в кеш L3 іншого чіплета - він ніби загальний

И напоследокWhat’s however a bit perplexing is that the core-to-core latencies between Gracemont cores is extremely slow, and that’s quite unintuitive as one would have expected coherency between them to be isolated purely on their local L2 cluster. Instead, what seems to be happening is that even between two cores in a cluster, requests have to travel out to the L3 ring, and come back to the very same pathway. That’s quite weird, and we don’t have a good explanation as to why Intel would do this.

Вот чтобы подобного, хоть и в меньших масштабах, не было, Интел и не делает несколько колец. Проще топология - всегда лучше.ronemun: ↑ 09.08.2022 23:47але віддалений з шаленою затримкою біля 80-120 нс

Лучше перефразировать:"затримки між ядрами Gracemont надзвичайно великі...". Это меньше вводит в заблуждение, не все сразу понимают, что медленные задержки (повільні затримки) это высокие задержки. Я, например, визуально аж "споткнулся" когда увидел слово slow там.ronemun: ↑ 10.08.2022 03:48 vmsolver

"Однак дещо дивує те, що затримки між ядрами Gracemont надзвичайно повільні, і це досить неінтуїтивно..."

Там же сказано, что они предполагают, что запросы даже внутри кластера наверное идут всё равно через кольцо, поэтому там так неоптимально получилось. В любом случае, я не думаю что так останется и в грядущем 13900. Хотя, е-ядра в многопотоке дают не плохую прибавку даже с подобными неоптимальностями, что говорит о стратегическом успехе всей задумки, даже не смотря на некоторые нюансы тактического уровня (надо меньше смотреть Арестовича).ronemun: ↑ 10.08.2022 03:48Тут важко розібратись в таких значних затримках. Хоча і логічно ніби якщо свій кеш дууже повільний

ronemun: ↑ 10.08.2022 03:48але тоді навіщо тратити так багато кешу (16 МБ в 13900) з такою малою користю.

Не знаю почему вы сделали подобный вывод, к кольцу соединён кеш L2, к которому по четырём независимым каналам подключены е-ядра, запросы от ядер идут в контроллер кеша L2, а вот он уже решает что делать дальше, искать у себя в тегах и одновременно послать запрос в "кольцо" (читать: в L3) или в какой-то последовательности, надо разбираться с политикой синхронизации.ronemun: ↑ 10.08.2022 03:48Виходить що е-ядра взагалі окремо вчеплені до основного кільця поза їх кеш L2, через свій хаб/кільце, тобто якби паралельно - одночасно станцією користується хтось один. Але тоді виходить що доступ в L3 (3МБ блок, 2-3 найближчих це 6-9 МБ) швидший ніж в L2 (4МБ на 4 ядра)І доступ до ядра в чужому кластері швидший. Напевно через вищі частоти в основному кільці і його ширину. Тоді ще більше шкода 16 МБ L2

Вот только на 7нм можно позволить себе кеш заметно больше и повысить производительность (== уменьшить простой железа на latеncy bound алгоритмах) много где, а небольшое увеличение задержек не сильно повлияет на общую картину.ronemun: ↑ 10.08.2022 03:48Якщо повернутись до схеми як у Xeon v3-4:

1. L2 кеш всього 0,25 - менша латентність. Кеш був інклюзивний - він моментально синхронізувався з L3. І це тянулось ще з 45 нм, отже на 7 нм взагалі не помітно.

О божечки в 13900 будет всего 14 станций (системный агент, 8 р-ядер, графика, четыре е-кластера), а вы про 24 говорите... Астанавитесь... (с)ronemun: ↑ 10.08.2022 03:482. 16 е-ядер + 4 блоків кешу L3 по 4 МБ + 4 на обмін це всього 24 станції, майже як в основному кільці: 8 р-ядер + 8 кеш + 4 обмін + DRAM +PCIe/DMI + графіка =23 (L3 по 4 МБ щоб зрівняти кількість з 13900 = 36 L3 +4*4=36+16=52). Дійсно, 2 великих кільця, тільки доступ між е-ядрами, а тут їх аж 16 штук, був би не за 50, а 30 нс, як в основному кільці.

Так 30 или 45-50?ronemun: ↑ 10.08.2022 03:48Але збільшились би між p- і е-ярами до 45-50, як у Xeon v4.

Нечего там разбирать, чем проще тем лучше, и Интел сделала как лучше.ronemun: ↑ 10.08.2022 03:48 Тут не розбереш що краще,

В шине там общая полоса важна, ядер же много.ronemun: ↑ 10.08.2022 03:48але думаю що обмін в основному буде йти між однаковими ядрами - немає сенсу між різними через 2 кратну різницю в продуктивності = частота х IPC (в 2,5 раз враховуючи гіпертрейдінг).

Считайте, что интеловцы сделали идеальное кольцо, как и любое идеальное железо оно несуществует, так и со вторым кольцом, его нет, но всё работаетronemun: ↑ 10.08.2022 03:48 Також друге кільце, можна робити вужчим у 2 рази через малу кількість кешу і повільніші ядра - адже загальна продуктивність його все одно у 2-3 рази меньша ніж у основного.

Посмотрим как сделают. В целом и то что сейчас катастрофой не является, но не хорошо конечно. С другой стороны это возможно следствие какой-то ошибки, которую в 13900 должны исправить.ronemun: ↑ 10.08.2022 03:48Хоча і зараз у частини е-ядер 40 нс між собою - в чужі кластери, а в 13900 їх буде аж 3 чужих

В Интел должны моделировать много разных вариантов и выбирать оптимальное, не злобные же они буратины для себя, а значит есть эффект предсказуемости в общих вещах.ronemun: ↑ 10.08.2022 03:48Але загалом в Інтел не погано зробили, тут ви праві, попарне зєднання p-ядер, при умові зменшення затримок між ними, теж гарна ідея

Не приписывайте мне

Ууу как пригорает, так мне не жалко, вот ещёronemun: ↑ 09.08.2022 23:47 8 низькофективних низькочастотних однопоточних ядер