Останні статті і огляди

Новини

Intel завершила розробку техпроцесів 20A та 18A

-

1nsane

Member

- Звідки: Ларнака, Кипр

Предлагаю обсудить Intel завершила розробку техпроцесів 20A та 18A

О, в Интеле снова включили генератор рандомных заявлений в розетку.

О, в Интеле снова включили генератор рандомных заявлений в розетку.

-

taras_cs

Member

- Звідки: Варшава-Київ-Дніпро

Які шоколадні обіцянки - спочатку +15% а потім ще +10% performance per watt

-

Devijack

Member

- Звідки: Запорожье

Интол розробили нову назву щоб не було стидно.

-

coffeeman

Member

- Звідки: Lviv

А що означають 2 нм та 1.8 нм? Ці ж процеси нібито ні до чого не прив'язані.

-

SergN

Member

- Звідки: Kyiv

Що тут значить слово "запуск"? Це ціла фабрика буде випускати продукцію на цьому техпроцесі? Там відразу акції компанії мали б добряче злетіти після такої новини, проте, якщо ні, то і трактування успіхів переоцінене.Розробка цього техпроцесу, судячи з усього, йде настільки гладко, що Intel перенесла його запуск з 2025-го на другу половину 2024 року.

-

taras_cs

Member

- Звідки: Варшава-Київ-Дніпро

Deleted

-

Евгений King

Member

- Звідки: Казна-де

А до чого прив'язані техпроцеси у TSMC чи Самсунга?? Правильно, ні до чого...coffeeman: ↑ 07.03.2023 12:34 А що означають 2 нм та 1.8 нм? Ці ж процеси нібито ні до чого не прив'язані.

Раніше техпроцес вказував довжину затвору транзистора

Зараз розмір техпроцесу це суцільний маркетинг, довжина затвору вже давно не відповідає техпроцесу і не сильно зменшується з прогресом техпроцесу

Сьогодні прогрессом можна вважати зростання щільності та енергоєфективності процесорів, і якщо покопатись у цьому напрямку - то можна побачити що прогрес сильно сповільняється

-

KimRomik

Member

это значит, что меряться будем ангстремами, и чем меньше оно, тем круче у того компcoffeeman: ↑ 07.03.2023 12:34 А що означають 2 нм та 1.8 нм? Ці ж процеси нібито ні до чого не прив'язані.

-

coffeeman

Member

- Звідки: Lviv

Ну так я й кажу - вже треба перестати тулити ці нанометри, бо одна частина інформації "про нанометри" - це маркетинг, інша - закрита інформація. Якщо при рівній продуктивності один процесор споживає вдвічі більше - то неважко здогадатися хто лідер.

-

dead_rat

Member

- Звідки: Берлін

Ну треба ж якось називати. Назовеш 7нм, то місцеві експерти плюватимуться, 5нм ну таке, а от 20А звучить свіжо і перспективноcoffeeman: ↑ 07.03.2023 12:34 А що означають 2 нм та 1.8 нм? Ці ж процеси нібито ні до чого не прив'язані.

-

Nikolay Yeryomenko

Member

В итоге главное чтобы потом не сказали: "ой извините надо подождать".

-

saren

Member

- Звідки: Днепр

coffeeman

самое смешное, имхо, проверить все эти дела практически невозможно.

Отправлено спустя 1 минуту 17 секунд:

Евгений King

мне очень интересно, на каком техпроцесса пробой между дорожками будет уже на 1В.

помнится у меня на 480 печи напруга на чипе была 0.98В.

самое смешное, имхо, проверить все эти дела практически невозможно.

Отправлено спустя 1 минуту 17 секунд:

Евгений King

мне очень интересно, на каком техпроцесса пробой между дорожками будет уже на 1В.

помнится у меня на 480 печи напруга на чипе была 0.98В.

-

lamer02

Member

Если не 20-30coffeeman: ↑ 07.03.2023 12:34 А що означають 2 нм та 1.8 нм? Ці ж процеси нібито ні до чого не прив'язані.

-

MetalistForever

Member

- Звідки: Харьков

-

manbearboar

Member

TSMC по сравнению с Интел более сейвово действует, не больше 1 крупной инновации за раз, поэтому у них лучше с выполнением графиков.

У Интел это всё может как взлететь, как и может повториться ситуация с 10нм, когда ещё пару лет понадобилось чтобы отладить для массового производства типа готовый техпроцесс.

Відправлено через 3 хвилини 1 секунду:

У Интел это всё может как взлететь, как и может повториться ситуация с 10нм, когда ещё пару лет понадобилось чтобы отладить для массового производства типа готовый техпроцесс.

Відправлено через 3 хвилини 1 секунду:

У TSMC привязано к характеристикам процессора ARM Cortex A7, реализованного на этом техпроцессе (симулированного).Евгений King: ↑ 07.03.2023 12:44 А до чого прив'язані техпроцеси у TSMC чи Самсунга?? Правильно, ні до чого...

-

ronemun

Advanced Member

легко провіряється: наприклад у АМД на 7 нм і у Інтел 7 абсолютно однакова площа 1 МБ кешу - 0,5 мм2. Можна тупо по фоткам кристалу вирахуватиsaren: ↑ 07.03.2023 19:11 coffeeman

самое смешное, имхо, проверить все эти дела практически невозможно.

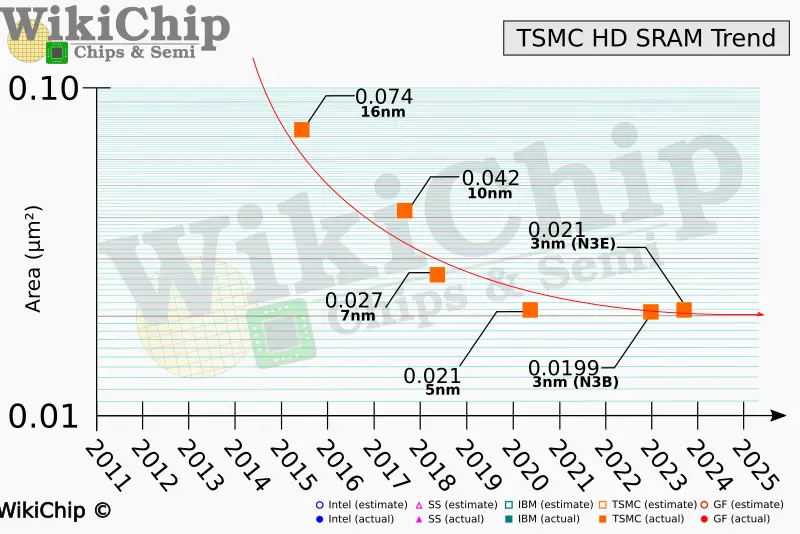

Згідно даних досліджень площа SRAM памяті падає прямопропорційно зменшеню техпроцесу - тобто при зменшенні з 7 до 4 нм площа SRAM зменшився десь в 1,7 раз. Тож в Інтел 20А площа SRAM буде ще в 2 рази меньша

Площа логіки зменшується не прямо, а майже в квадраті, але логіка різна, тож тут важко сказати яка площа якої логіки має бути.

Як недивно площа інтерфейсів тої ж версії, наприклад PCIe v4 чи v5, чи DRAM зменшується краще ніж SRAM, а оскільки ці блоки добре видно на фотці кристалу то їх можна спокійно порівняти. Але головне щоб версії були тіж, томущо між ними є сильна різниця на тому ж техпроцесі: SerDes PCIe v5 займає у 2 рази більшу площу ніж v3, і у 1,5 рази ніж v4

-

manbearboar

Member

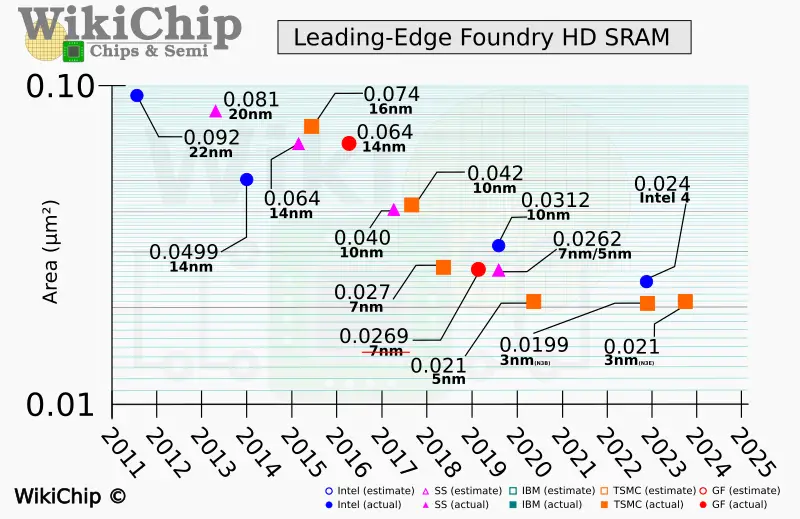

https://fuse.wikichip.org/news/7343/ied ... h-of-sram/ronemun: ↑ 08.03.2023 00:39 Згідно даних досліджень площа SRAM памяті падає прямопропорційно зменшеню техпроцесу - тобто при зменшенні з 7 до 4 нм площа SRAM зменшився десь в 1,7 раз.

SRAM практически всё, не масштабируется дальше.

При чём Intel 4 где-то ближе к TSMC 5.

- спойлер

-

-

l-m

Member

manbearboar

Які ти цікаві картинки постиш

Шкода вони сильно суперечать твоїй вірі, що неможливо досягти щільності в 133 млн транзисторів на мм2

Простою арифметикою дізнаємось з цих даних теоретичну щільність SRAM без будь-якої додаткової логіки для 7нм ТSMC — 1/0.027*6 = 222 млн/мм2.

Але без додаткової логіки вона працювати не буде, тому навіть на кристалі з 3Д-кешем, де сильно зекономили на інтерконектах, маємо тільки 133 млн/мм2, які тобі здались неможливими, та почались вигадування ще одного поверху (про який би неодмінно похвалились, якби він справді там був)

Які ти цікаві картинки постиш

Шкода вони сильно суперечать твоїй вірі, що неможливо досягти щільності в 133 млн транзисторів на мм2

- спойлер

- manbearboar: ↑ 06.03.2023 21:36

Максимальная плотность для HP версии 7нм техпроцесса - это 50-60 миллонов, никак не 133млн.l-m: ↑ 06.03.2023 18:47 Сам по собі чисто кеш, як срам пам'ять дозволяє отримати максимальну щільність транзисторів.

У Интел в Рапторе ещё меньше, где-то в районе 40-50млн.

Самые плотные девайсы на 7нм имеют под 100млн/мм2, но это мобильные чипы, которым не нужно развивать 5.25Ггц частоты, а именно такую частоту эта нашлёпка развивает.

В общем 133млн в одном слое это анриал, там 2 этажа по 60млн.

Простою арифметикою дізнаємось з цих даних теоретичну щільність SRAM без будь-якої додаткової логіки для 7нм ТSMC — 1/0.027*6 = 222 млн/мм2.

Але без додаткової логіки вона працювати не буде, тому навіть на кристалі з 3Д-кешем, де сильно зекономили на інтерконектах, маємо тільки 133 млн/мм2, які тобі здались неможливими, та почались вигадування ще одного поверху (про який би неодмінно похвалились, якби він справді там був)

-

ronemun

Advanced Member

manbearboar

графік виглядає дійсно тупіковим, якби не один нюанс - тупік в TSMC, в Інтела все нормально

По друге в логарифмічній шкалі, і то з основою аж 10, далі буде все тільки плоским, адже чим нижче по шкалі таж відстань вимагатиме в рази більшого результату, а я писав що зменшення йде ЛІНІЙНО.

Хоча SRAM дійсно далі не вигідно буде випускати на малих техпроцесах - ціна площі пластин росте значно швидше ніж кількість SRAM на ній, саме тому АМД 64 МБ кристали далі випускає на 7 нм. На щастя, є способи зєднати навіть кеш L3, а L2 займає мало

Ну і самі комірки це ще не все - флеш память теж комірки не сильно зменьшиш, адже заряд почне розмоктуватись, але чомусь густина виросла в рази, при тому кількість зарядів в комірці виросла з 2х до 4х. Там багато слоїв, так само і зі SRAM може зроблять. Комірку флеш змогли перевести з великої плоскої в маленьку по площі, але більшу в обємі ніж раніше, а логіка мініатюрна під коміркою. Значно тоньша і глибша металізація дозволила це обєднати. І хоча обслуговуюча логіка сильно ускладнилась, загальна площа на порядок меньша, а надійність і швидкість лише зросла

графік виглядає дійсно тупіковим, якби не один нюанс - тупік в TSMC, в Інтела все нормально

По друге в логарифмічній шкалі, і то з основою аж 10, далі буде все тільки плоским, адже чим нижче по шкалі таж відстань вимагатиме в рази більшого результату, а я писав що зменшення йде ЛІНІЙНО.

Хоча SRAM дійсно далі не вигідно буде випускати на малих техпроцесах - ціна площі пластин росте значно швидше ніж кількість SRAM на ній, саме тому АМД 64 МБ кристали далі випускає на 7 нм. На щастя, є способи зєднати навіть кеш L3, а L2 займає мало

Ну і самі комірки це ще не все - флеш память теж комірки не сильно зменьшиш, адже заряд почне розмоктуватись, але чомусь густина виросла в рази, при тому кількість зарядів в комірці виросла з 2х до 4х. Там багато слоїв, так само і зі SRAM може зроблять. Комірку флеш змогли перевести з великої плоскої в маленьку по площі, але більшу в обємі ніж раніше, а логіка мініатюрна під коміркою. Значно тоньша і глибша металізація дозволила це обєднати. І хоча обслуговуюча логіка сильно ускладнилась, загальна площа на порядок меньша, а надійність і швидкість лише зросла

-

ender

Member

- Звідки: Украина

Не совсем верно по поводу "Згідно даних досліджень".ronemun: ↑ 08.03.2023 00:39легко провіряється: наприклад у АМД на 7 нм і у Інтел 7 абсолютно однакова площа 1 МБ кешу - 0,5 мм2. Можна тупо по фоткам кристалу вирахуватиsaren: ↑ 07.03.2023 19:11 coffeeman

самое смешное, имхо, проверить все эти дела практически невозможно.

Згідно даних досліджень площа SRAM памяті падає прямопропорційно зменшеню техпроцесу - тобто при зменшенні з 7 до 4 нм площа SRAM зменшився десь в 1,7 раз. Тож в Інтел 20А площа SRAM буде ще в 2 рази меньша

Площа логіки зменшується не прямо, а майже в квадраті, але логіка різна, тож тут важко сказати яка площа якої логіки має бути.

Як недивно площа інтерфейсів тої ж версії, наприклад PCIe v4 чи v5, чи DRAM зменшується краще ніж SRAM, а оскільки ці блоки добре видно на фотці кристалу то їх можна спокійно порівняти. Але головне щоб версії були тіж, томущо між ними є сильна різниця на тому ж техпроцесі: SerDes PCIe v5 займає у 2 рази більшу площу ніж v3, і у 1,5 рази ніж v4

Не площадь памяти уменьшается пропорционально уменьшению техпроцеса, а техпроцес называют пропорционально увеличению плотности (уменьшению площади памяти).

Поэтому у Intel были проблемы с неймингом до этого - их цифры означали некий физический размер, в то время как конкуренты называли техпроцес относительно какого-то древнего техпроцеса с определённой плотностью транзисторов.

PS: если у Intel реально будет рабочие так называемые 2нм и 1.8нм техпроцесы то это заявка на приличный скачок в развитии технологий. Конкуренция на рынке интенсицифируется. Глядишь и дефицит чипов победят

upd: вижу уже всё разжевали.. мой некропостинг ни к чему