Пошук дав 1506 результатів

- 18.04.2024 20:40

Никто так и не порадуется за рынок AI-ускорителей? Увеличат шину на один корпус до 2048 бит, экв.частота 9.8 ГГц, 2.5 ТБ/с полосы при ёмкости 36 ГБ. Отношение полосы к объему 69.7, например у RTX 4070 этот параметр 42 (многозначительно-то как! :rotate: ), что означает баланс отношения полосы к объем...

- 18.04.2024 10:41

Всего +8% рынка за три года? С застоем в новых техпроцессах? А разговоров то было (с)

- 17.04.2024 19:50

Тобто залізо та ПЗ будуть бачити звичайний кеш L3 обсягом 96 МБ, а не eDRAM L4 як це було у того ж Intel Broadwell. Буквоедство какое-то, eDRAM L4 кеш в Broadwell с точки "зрения" железа и ПО это обычный LLC кеш, акцент на том что он eDRAM совершенно излишний. Однак тепер в розпорядженні користувач...

- 17.04.2024 09:29

AssayMAS То трансформаторы и двигатели, а здесь обычный коннектор. Ну вы и сравнили, энергетику третьего пня с 600 Вт коннектором :rotate: Почему не всегда ставят предохранители вопрос широкий, но вряд ли это имеет отношение к разъему. Слушайте, вот эти костыли в виде обвешивания защитами изделия, ...

- 16.04.2024 18:48

ДядяСаша Только сейчас заметил, что в самом первом своём посте ошибочно написал L2, там L3 конечно же. Я всё время говорил про LP. Возможно L2 есть, но про него не удосужились написать по какой-то причине, но L3 у графики свой, выше цитата с anandtech. Да и объем 3.8 МБ прям вообще не типичный, это...

- 16.04.2024 18:41

Не путай свои маразмы с анандтекомScoffer: ↑ 16.04.2024 18:17Бігом штудувати документацію, а не маразми з анандтеку

Всё он верно показал. Оно шире структурно, но уже поблочно, если бы ты читал документацию то не сочинял бы ерунду

- 16.04.2024 18:14

Схема 2Е ядер (вони об'єднані в кластер 2+2 через Л2кеш і шину): Вы сказочный этот, как его, сказочник :lol: На картинке одно ядро :laugh: Front End The big item about the Tremont front end of the core was the move to dual three-wide decode paths , enabling two concurrent streams of decode that cou...

- 16.04.2024 17:13

Всё течёт, всё меняется, даже кеш у встроенной графики интелаScoffer: ↑ 16.04.2024 15:21До речі цей шарений кеш у інтела ще з народження їхньої вбудованої графіки

- 16.04.2024 15:45

Sanc Перечитайте ещё раз мой пост, там сказано про какой прогресс идёт речь. И не лень было этот поток сознания писать? У EUV как раз зеркала, диэлектрические. DUV lithography machines use lenses to focus light. But there are no lenses for EUV lithography. Since most materials absorb EUV light, the...

- 16.04.2024 14:55

Ну да, інтел не обнуляє верхні частини регістрів при <64бітних обчисленнях Он их просто не использует если для операции они не нужны, ты на ровном месте придумываешь нерелевантные примеры, отключать 32 бита на пару тактов никто не будет, не говоря уже о том, что не нужно путать архитектурные регист...

- 16.04.2024 14:41

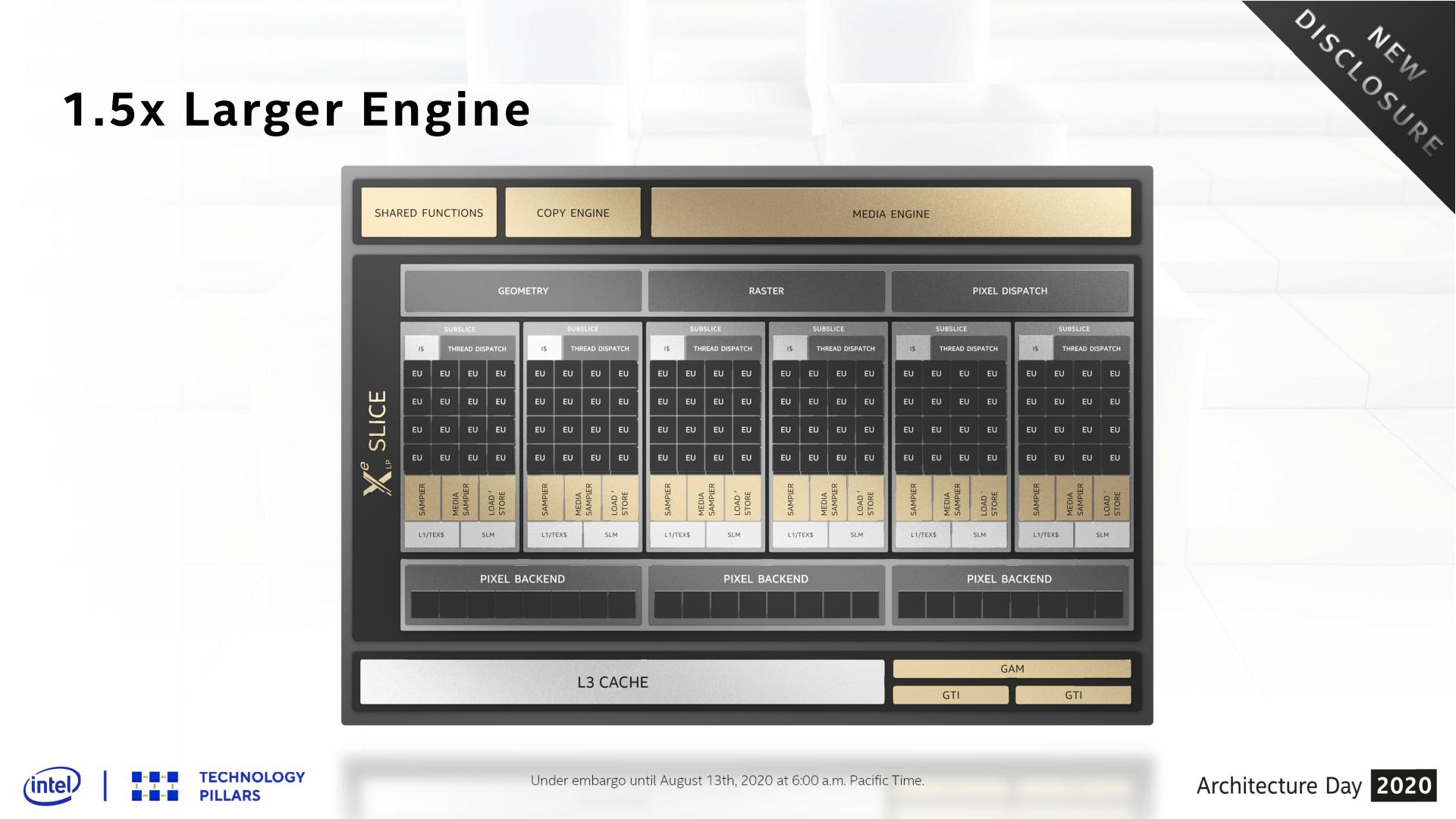

Раз є л3 на відеокарті, то покажи буть ласка де там є л2. Кеші нумеруються послідовно :rotate: Нумерация кешей это дело интела, вот у него и спрашивай :rotate: На слайде нарисован отдельный L3, значит это свой кеш с таким именем, если бы использовался общий L3, то зачем его там рисовать, если его т...

- 16.04.2024 14:32

Scoffer Я другой слайд видел, что L3 это отдельный кеш GPU, да и у ананда прямо пишут The on-GPU L3 cache ( not to be confused with Tiger Lake’s shared Last Level Cache ) has also undergone its own upgrades, receiving both a capacity and a bandwidth boost. On the capacity front, the L3 cache can no...

- 16.04.2024 13:50

Scoffer

Это твои выдумки. Там ничего про цпушный L3 не пишут, выше полное предложение, internal L3 это гпушный L3.

Это твои выдумки. Там ничего про цпушный L3 не пишут, выше полное предложение, internal L3 это гпушный L3.

- 16.04.2024 13:41

Scoffer Отключают и питание, не выдумывай. Блоки, котрі не використовуються - не тактуються Гениально! Что же ты молчал, ибо никто не догадывался отключать тактирование :lol: Логика после старта сидит в логическом ресете, а когда питание пришло в норму, о чём заботиться один из блоков ИС, он даёт р...

- 16.04.2024 13:21

У GPU есть свой L3 кеш и к процовому L3 он отношения не имеет, это разные кешиScoffer: ↑ 16.04.2024 12:44 vmsolver

Слайс має L3, котрий і є оте шарене з L3 проца що розпізнає сандра як L2

- спойлер

Ты свою картинку хоть бы посмотрел

- 16.04.2024 13:17

Так Е-ядра це уже альтернатива НТ, там де є 8 Е-ядер відключення НТ дає буст ФПС. Нет, это не альтернатива Погугліть схему Е-ядер і побачите, що там кластер 2Е+2Е з спільним Л2, а самі Е- ядра це сіамські близнюки як АМД Бульдозер Мне не надо гуглить, я помню кластер и в нём четыре независимых ядра...

- 16.04.2024 13:08

Kashtan Тут важно за счет чего обыграл, если за счет скорости микроконтроля, на которую человек не способен в такой же степени как компьютер, то это одно, а если за счет построения сильных ходов, стратегий и тактик, то это другое. В Го, такое впечатление, выиграли за счет большого количества партий...

- 16.04.2024 12:13

Scoffer Полное предложение там такое: Although the OpenCL routine returns the presence of 64 kB of Shared Memory on Intel Xe (in opposition to 48 kB in Nvidia), it seems like this memory is mapped to the internal L3 cache memory which is slower than the classical SM used in external GPUs it это Sha...

- 16.04.2024 11:56

Реалізація НТ і АВХ512 жруть в пасиві фактом своєї наявності: займають місце, оптимізація якого допомогла би укоротити конвеєр, зменшити розмір ядра і сигнальних шляхів, що некисло бафнуло би ІРС. Подивіться на проци де є АВХ512 але виключено і де його нема фізично: різниця в жорі по ядру приведено...

- 15.04.2024 15:45

Scoffer

Вот выйдут процы и посмотришь, а тратить время на споры с тобой о том, чего ты не понимаешь, мне не интересно

Вот выйдут процы и посмотришь, а тратить время на споры с тобой о том, чего ты не понимаешь, мне не интересно